A Novel Approach for Integrated Shortest Path Finding Algorithm (ISPSA) Using Mesh Topologies and Networks-on-Chip (NOC)

Main Article Content

Abstract

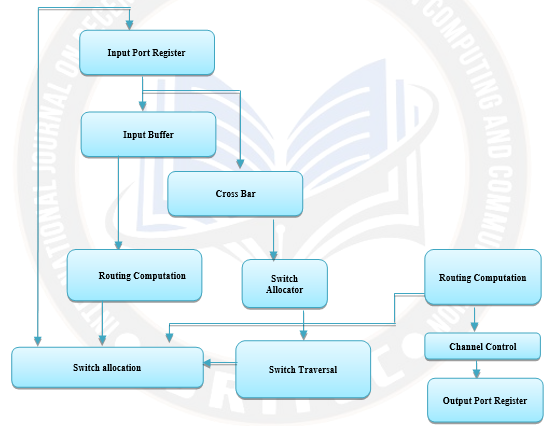

A novel data dispatching or communication technique based on circulating networks of any network IP is suggested for multi data transmission in multiprocessor systems using Networks-On-Chip (NoC). In wireless communication network management have some negatives have heavy data losses and traffic of data sending data while packet scheduling and low performance in the varied network due to workloads. To overcome the drawbacks, in this method proposed system is Integrated Shortest Path Search Algorithm (ISPSA) using mesh topologies. The message is sent to IP (Internet Protocol) in the network until the specified bus accepts it. Integrated Shortest Path Search Algorithm for communication between two nodes is possible at any one moment. On-chip wireless communications operating at specific frequencies are the most capable option for overcoming metal interconnects multi-hop delay and excessive power consumption in Network-on-Chip (NoC) devices. Each node can be indicated by a pair of coordinates (level, position), where the level is the tree's vertical level and the view point is its horizontal arrangement in the sequence of left to right. The output gateway node's n nodes are linked to two nodes in the following level, with all resource nodes located at the bottommost vertical level and the constraint of this topology is its narrow bisection area. The software Xilinx 14.5 tool by using that overall performance analysis of mesh topology, each method are reduced data losses with better accuracy although the productivity of the delay is decreased by 21 % was evaluated and calculated..

Article Details

References

J. G. Pandey, T. Goel, M. Nayak, C. Mitharwal, A. Karmakar and R. Singh, “A high-performance VLSI architecture of the present cypher and its implementations for SoCs”, 31st IEEE International System-on-Chip Conference (SOCC), pp. 96-101, 2018.

Shivdeep, A. Biswas, S. Ghosh, T. Nag, S. P. Maity and H. Rahaman, “HLS based implementation of modified DE-RIW algorithm on FPGA and P-SoC”, IEEE 1st International Conference for Convergence in Engineering (ICCE), pp. 439-443, 2020.

M. Bahadori and K. Järvinen, “A programmable SOC-based accelerator for privacy-enhancing technologies and functional encryption”, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 10, pp. 2182-2195, 2020.

A. Sánchez, Y. Barrios, L. Santos and R. Sarmiento, “Evaluation of TMR effectiveness for soft error mitigation in SHyLoC compression IP core implemented on Zynq SoC under heavy ion radiation”, IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pp. 1-4, 2019.

R. Mamarde and S. Khoje, “Implementing PSK and FSK Scheme in Zynq-7000 FPGA for SDR Applications”, Second international conference on intelligent computing and control systems (ICICCS), pp. 721-727, 2018.

X. Xiang, P. Sigdel and N. -F. Tzeng, “Buffer-less network-on-chips with bridged multiple subnetworks for deflection reduction and energy Savings”, in IEEE Transactions on Computers, vol. 69, no. 4, pp. 577-590, 2020.

G. D. Vani, M. Chinnaiah and S. R. Karumuri, “Hardware scheme for autonomous docking algorithm using FPGA based mobile robot”, 8th International Symposium on Embedded Computing and System Design (ISED), pp. 110-115, 2018.

S. Shahabuddin, I. Hautala, M. Juntti and C. Studer, “ADMM-based infinity-norm detection for massive MIMO: algorithm and VLSI Architecture”, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 29, no. 4, pp. 747-759, 2021.

A. Singh, S. Pratap Singh, M. Lakshmanan and V. K. Pandey, “Gain and delay simulation for molecular communication using Verilog”, 2nd International Conference on Advances in Computing, Communication Control and Networking (ICACCCN), pp. 430-433, 2020.

S. F. Sultana and B. Patil, “Area efficient VLSI architecture for reversible radix_2 FFT algorithm”, International Conference on Emerging Smart Computing and Informatics (ESCI), 2021, pp. 136-141, 2021.

S. Haider and V. Tiwari, “VLSI architecture for high tap if a filter with low complexity using multi-rate approach”, International Conference on Artificial Intelligence and Smart Systems (ICAIS), pp. 1479-1482, 2021.

D. Deepa and C. N. Marimuthu, “VLSI Design of a squaring architecture based on yavadunam sutra of Vedic mathematics”, International Conference on Electronics and Sustainable Communication Systems (ICESC), pp. 1162-1167, 2020.

A. Xu, J. Zhang, M. -K. Law, X. Zhao, P. -I. Mak and R. P. Martins, “An N × N Multiplier-Based Multi-Bit strong PUF using path delay extraction”, IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, 2020.

A. Purohit, M. R. Ahmed and R. V. S. Reddy, “Design of area optimized arithmetic and logical unit for microcontroller”, IEEE VLSI device circuit and system (VLSI DCS), pp. 335-339, 2020.

S. Shahabuddin, I. Hautala, M. Juntti and C. Studer, “ADMM-Based infinity-norm detection for massive MIMO: algorithm and VLSI Architecture”, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 29, no. 4, pp. 747-759, 2021.

Y. Parmar and K. Sridharan, “A high-performance VLSI architecture for a self-feedback convolutional neural network”, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 68, no. 1, pp. 456-460, and 2021.

R. Gomathi, S. Gopalakrishnan, S. Ravi Chand, S. Selvakumaran, J. JeffinGracewell, Kalivaraprasad. B, “Design and speed analysis of low power single and double edge triggered flip flop with pulse signal feed-through Scheme”,IJEER, no. 10(4), pp. 1107-1114, 2022, DOI: 10.37391/IJEER.100456.

Taha Rashid, Mohammed Rasheed, Muhammad AbdelhadiSarhan, Ahmed Shawki Jaber, Mustafa NuhadAldaraji, Tarek Saidani, Ahmed Rashid, “Folded cascode operational amplifier design utilizing 0.25 µm CMOS technology”, Al-Salam Journal for Engineering and Technology, vol. 2, no. 1, 2023.

Rana Talib, Shatha Talib Rashid, Noora Saleem Jumaah, Rusul Sabah, “A design neural database to identify the problem of the conditions in dental clinics”, Al-Salam Journal for Engineering and Technology, vol. 1, no. 2, 2022.