Design of Multiplexers using Reversible Logic Technique

Main Article Content

Abstract

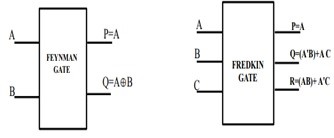

Reversible logic is promising as it can be applied to different applications in low power like nanocomputing especially in quantum computing. Reversible logic is a technioue for power reduction. Reversible circuits are similar to digital circuits but they work using reversible logic gates. This study focuses on reducing the garbage output and ancilla inputs in reversible multiplexers, thereby reducing the power consumption. In this study two designs of Multiplexers are given. Design1 is using TwinSJ gate and AJ gate. 2:1, 4:1 and 8:1 multiplexers are built. In Design 2, a new gate (SJ gate) is built which functions as 2:1 multiplexer. It has 4*4 configuration. The inputs are suitably configured so that it performs various logic functions. Using this SJ gate and other basic reversible logic gates, 2:1, 4:1 and 8:1 multiplexers are built. In 2:1 multiplexer, Ancilla inputs are improved to '0' from 5 and garbage output has been reduced to 2 against 7 in existing design. 4:1 multiplexers are built with ‘0’ ancilla inputs against 2 and 11 in existing designs. Garbage output of the proposed 4:1 multiplexer is 5 against 6 and 16 in existing designs. 8:1 multiplexer is built with 1 ancilla input and 11 garbage output against 2 and 12 respectively in existing design. This is designed using VHDL code - xilinx 14.7 for verification purpose and simulated on ISIM.

Article Details

References

C.H. Bennett, “Logical Reversibility of computation,” IBM Journal of Research and Development, pp 525-532, 1973.

R. Landauer, “Irreversibility and heat generation in the computing process,” IBM Journal of Research and Development, vol. 5, pp. 183-191, 1961.

D. Goyal, and V. Sharma, VHDL Implementation of Reversible Logic Gates Journal of Advanced Technology & Engineering Research (IJATER) vol. 2, no. 3, May. 2012.

S. Gugnani, and A. Kumar, “Synthesis of Reversible Multiplexers,” International Journal of Scientific & Engineering Research, vol. 4, no. 7, p. 1859, Jul. 2013.

V. Shukla, O. P. Singh, G. R. Mishra, and R. K. Tiwari, “An Optimized Circuit of 8:1 Multiplexer Circuit using Reversible Logic Gates,” International Journal of Computer Applications (0975 – 8887) International Conference on Communication, Computing and Information Technology (ICCCMIT-2014).

S. Mamataj, B. Das, A. Rahaman, “Realization of Different Multiplexers by Using COG Reversible Gate,” International Journal of Electronics and Electrical Engineering, vol. 3, no. 5, Oct. 2015

N.Pannu, and N. R.Prakash, “A Power-Efcient Multiplexer using Reversible Logic,” Microelectronics Journal (ELSEVIER), vol. 53, pp. 25–34, 2016. Indian Journal of Science and Technology, vol. 9, no. 30, Aug. 2016.

J. N. Ravi, A. M. Vijay Prakash, S. Madan, “Design and Implementation of Digital Components Using Reversible Logic Gates,” International Journal of Technical Research & Science (IJTRS), p. 70, Mar. 2017.

S. Mann, and R. Jain, “Design and Analysis of Reversible Multiplexer and Demultiplexer using R-Gates,” Proceeding International conference on Recent Innovations is Signal Processing and Embedded Systems (RISE -2017), pp. 27-29 Oct. 2017

G. Sreekanth, C. Venkata Sudhakar, “Design and Synthesis of Combinational Circuits using Reversible Logic,” International Journal of Electronics, Electrical and Computational System IJEECS, vol. 7, no. 4 Apr. 2018.

A. M. Chabi, A. Roohi, H. Khademolhosseini, S. Sheikhfaal, S. Angizi, K. Navi, and R. F. DeMara, Towards ultra-efficient QCA reversible circuits,” Microprocessors and Microsystems, vol. 49, Mar. 2017, pp. 127-138

H. M. Gaur, A.K. Singh, and U. Ghanekar, “In-depth Comparative Analysis of Reversible Gates for DesigningLogic Circuits,” Procedia Computer Science, vol. 125, pp. 810-817, 2018, 6th International Conference on Smart Computing & Communications.

D. Krishnavenia, M. Geetha Priya, “Design of a new BUS for low power reversible computation,” Computers and Electrical Engineering, vol. 89, p. 106938, 2021.

A.K. Rajput, S. Chouhan, M. Pattanaik, “Low Power Boolean Logic Circuits using Reversible Logic Gates Auckland University of Technology,” 2019 International Conference on Advances in Computing, Communication and Control (ICAC3)-IEEE Xplore, Mar. 2020.

A. P. Sooriamala, A.K. Thomas, R. Korah, “Study On Reversible Logic Circuits And Analysis,” Alliance International Conference on Artificial Intelligence and Machine Learning (AICAAM), Apr. 2019.

A.P. Sooriamala, A.K. Thomas, R. Korah, "Reduction of Garbage Outputs and Constant Inputs in Design of Combinational Circuits Using Reversible Logic," 2021 Sixth International Conference on WirelessCommunications, Signal Proc.essing and Networking (WiSPNET), 2021.

A. P. Sooriamala, A.K. Thomas, R. Korah, “Design And Study Of Circuits Using Reversible Logic,” IEEE 2nd International Conference on Electronics and Sustainable Communication Systems ICESC, pp. 4-6, Aug. 2021.

Wiling, B. (2021). Locust Genetic Image Processing Classification Model-Based Brain Tumor Classification in MRI Images for Early Diagnosis. Machine Learning Applications in Engineering Education and Management, 1(1), 19–23. Retrieved from http://yashikajournals.com/index.php/mlaeem/article/view/6

K.C. Koteswaramma, A. Shreya, N.H. Vardhan, K. Tarun, S.C. Venkateswarlu, and V. Vijay, “ASIC Implementation of division circuit using reversible logic gates applicable in ALUs,” In Innovations in Signal Processing and Embedded Systems, Springer, Singapore pp. 119-132, 2023.

G. V. Vinod, D.V. Kumar and N. M. Ramalingeswararao, “An Innovative Design of Decoder Circuit using Reversible Logic,” Journal of VLSI circuits and systems, vol. 4, no. 01, pp.1-6, 2022.

S. S. Samrin, R. Patil, S. Itagi, S.C. Chetti, and A. Tasneem, Design of Logic Gates using Reversible Gates with Reduced Quantum Cost. Global Transitions Proceedings. 2022.