A Brand-New, Area - Efficient Architecture for the FFT Algorithm Designed for Implementation of FPGAs

Main Article Content

Abstract

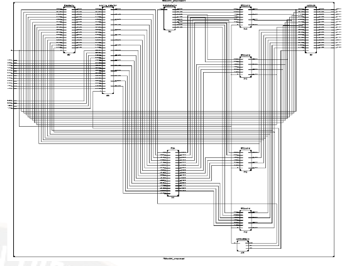

Elliptic curve cryptography, which is more commonly referred to by its acronym ECC, is widely regarded as one of the most effective new forms of cryptography developed in recent times. This is primarily due to the fact that elliptic curve cryptography utilises excellent performance across a wide range of hardware configurations in addition to having shorter key lengths. A High Throughput Multiplier design was described for Elliptic Cryptographic applications that are dependent on concurrent computations. A Proposed (Carry-Select) Division Architecture is explained and proposed throughout the whole of this work. Because of the carry-select architecture that was discussed in this article, the functionality of the divider has been significantly enhanced. The adder carry chain is reduced in length by this design by a factor of two, however this comes at the expense of additional adders and control. When it comes to designs for high throughput FFT, the total number of butterfly units that are implemented is what determines the amount of space that is needed by an FFT processor. In addition to blocks that may either add or subtract numbers, each butterfly unit also features blocks that can multiply numbers. The size of the region that is covered by these dual mathematical blocks is decided by the bit resolution of the models. When the bit resolution is increased, the area will also increase. The standard FFT approach requires that each stage contain times as many butterfly units as the stage before it. This requirement must be met before moving on to the next stage.

Article Details

References

C. A. Lara-Nino, A. Diaz-Perez and M. Morales-Sandoval, “Elliptic Curve Lightweight Cryptography: A Survey,” in IEEE Access, vol. 6, pp. 72514-72550, 2018, doi: 10.1109/ACCESS.2018.2881444.

Rivest RL, Shamir A, Adleman L. A Method for Obtaining Digital Signatures and Public-key Cryptosystems. Commun. ACM. Feb. 1978; 21(2): 120-126. https://doi.org/10.1145/359340.359342 3. Kong Y, Asif S, Khan Mohammad AU. Modular multiplication using the core function in the residue number system. AAECC. Springer Berlin Heidelberg. Jan. 2015; 27(1): 1±16.

N. Koblitz, “Elliptic curve cryptosystems,” Math. Comput., vol. 48, no. 177, pp. 203–209, 1987.

V. S. Miller, “Use of elliptic curves in cryptography,” in Proc. Conf. Theory Appl. Cryptograph. Techn. Santa Barbara, CA, USA: Springer, 1985, pp. 417–426.

Hankerson Darrel, Menezes Alfred J, Vanstone Scott. Guide to Elliptic Curve Cryptography. Springer-Verlag New York, Inc. Jan. 2003.

IEEE Standard Specifications for Public-Key Cryptography. IEEE Standard 1363-2000. Aug. 2000; pp:1±228.

NIST- National Institute of Standards and Technology, Digital Signature Standard. FIPS Publication 186-2. 2000.

J. W. Bos, J. A. Halderman, N. Heninger, J. Moore, M. Naehrig, and E. Wustrow, “Elliptic curve cryptography in practice,” in Proc. Int. Conf. Financial Cryptogr. Data Secur. Christ Church, Barbados: Springer, 2014, pp. 157–175.

G. M. de Dormale and J.-J. Quisquater, “High-speed hardware implementations of elliptic curve cryptography: A survey,” J. Syst. Archit., vol. 53, nos. 2–3, pp. 72–84, 2007.

H. Asshidiq, A. Sasongko and Y. Kurniawan, “Implementation of ECC on Reconfigurable FPGA Using Hard Processor System,” 2018 International Symposium on Electronics and Smart Devices (ISESD), Bandung, 2018, pp. 1-6, doi: 10.1109/ISESD.2018.8605444.

M. Bedoui, B. Bouallegue, B. Hamdi and M. Machhout, “An Efficient Fault Detection Method for Elliptic Curve Scalar Multiplication Montgomery Algorithm,” 2019 IEEE International Conference on Design & Test of Integrated Micro & Nano-Systems (DTS), Gammarth-Tunis, Tunisia, 2019, pp. 1-5, doi: 10.1109/DTSS.2019.8914743.

P. Ahuja, H. Soni and K. Bhavsar, “High Performance Vedic Approach for Data Security Using Elliptic Curve Cryptography on FPGA,” 2018 2nd International Conference on Trends in Electronics and Informatics (ICOEI), Tirunelveli, 2018, pp. 187-192, doi: 10.1109/ICOEI.2018.8553721

V. Maruthi Prasad, B. Bharathi, “A Novel Trust Negotiation Protocol for Analysing and Approving IoT Edge Computing Devices Using Machine Learning Algorithm”, International Journal of Computer Networks and Applications (IJCNA), 9(6),PP: 712-723, 2022, DOI: 10.22247/ijcna/2022/217704.

M. M. Islam, M. S. Hossain, M. Shahjalal, M. K. Hasan and Y. M. Jang, “Area-Time Efficient Hardware Implementation of Modular Multiplication for Elliptic Curve Cryptography,” in IEEE Access, vol. 8, pp. 73898-73906, 2020, doi: 10.1109/ACCESS.2020.2988379.

Rashid, Muhammad & Imran, Malik & Jafri, Atif & Kashif, Muhammad. (2019). A Throughput/Area Optimized Pipelined Architecture for Elliptic Curve Crypto Processor. IET Computers & Digital Techniques. 13. 10.1049/iet-cdt.2018.5056.

M. M. Islam, M. S. Hossain, M. K. Hasan, M. Shahjalal and Y. M. Jang, “FPGA Implementation of High-Speed Area-Efficient Processor for Elliptic Curve Point Multiplication Over Prime Field,” in IEEE Access, vol. 7, pp. 178811-178826, 2019, doi: 10.1109/ACCESS.2019.2958491.

H. N. Almajed and A. S. Almogren, “SE-Enc: A Secure and Efficient Encoding Scheme Using Elliptic Curve Cryptography,” in IEEE Access, vol. 7, pp. 175865-175878, 2019, doi: 10.1109/ACCESS.2019.2957943.

R. Salarifard and S. Bayat-Sarmadi, “An Efficient Low-Latency Point-Multiplication Over Curve25519,” in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 10, pp. 3854-3862, Oct. 2019, doi: 10.1109/TCSI.2019.2914247.

P. Choi, M. Lee, J. Kim and D. K. Kim, “Low-Complexity Elliptic Curve Cryptography Processor Based on Configurable Partial Modular Reduction Over NIST Prime Fields,” in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 65, no. 11, pp. 1703-1707, Nov. 2018, doi: 10.1109/TCSII.2017.2756680.

Orlando G and Paar C. A High-Performance Reconfigurable Elliptic Curve Processor for GF(2m). In:Proc. CHESS. 2000. pp: 41±56.

D. F. P. Gallagher and C. Director, “FIPS PUB 186-3 federal information processing standards publication digital signature standard (DSS),” Federal Inf. Process. Standards Publication, 2009.

C. Rebeiro, S. S. Roy, and D. Mukhopadhyay, “Pushing the limits of high-speed GF(2m) elliptic curve scalar multiplication on FPGAs,” in Proc. Int. Workshop CHES, 2012, pp. 494–511.

R. Azarderakhsh and A. Reyhani-Masoleh, “Efficient FPGA implementations of point multiplication on binary Edwards and generalized Hessian curves using Gaussian normal basis,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 8, pp. 1453–1466, Aug. 2012.

S. S. Roy, C. Rebeiro, and D. Mukhopadhyay, “Theoretical modelling of elliptic curve scalar multiplier on LUT-based FPGAS for area and speed,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 21, no. 5, pp. 901–909, May 2013.

G. D. Sutter, J. Deschamps, and J. L. Imaña, “Efficient elliptic curve point multiplication using digit-serial binary field operations,” IEEE Trans. Ind. Electron., vol. 60, no. 1, pp. 217–225, Jan. 2013.

K. C. C. Loi, S. An, and S.-B. Ko, “FPGA implementation of low latency scalable elliptic curve cryptosystem processor in GF(2m),” in Proc. ISCAS, Jun. 2014, pp. 822–825.

Z.-U.-A. Khan and M. Benaissa, “Throughput/area-efficient ECC processor using montgomery point multiplication on FPGA,” IEEE Trans. Circuits Syst. II, Express Briefs, vol. 62, no. 11, pp. 1078–1082, Nov. 2016.

L. Li and S. Li, “High-performance pipelined architecture of elliptic curve scalar multiplication over GF(2m),” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 24, no. 4, pp. 1223–1232, Apr. 2016.

T. T. Nguyen and H. Lee, “Efficient algorithm and architecture for elliptic curve cryptographic processor,” J. Semicond. Technol. Sci., vol. 16, no. 1, pp. 118–125, 2016.

B. Rashidi, R. R. Farashahi, and S. M. Sayedi, “High-speed hardware architecture of scalar multiplication for binary elliptic curve cryptosystems,” in Proc. IEEE Conf. Inf. Secur. Cryptol. (ISCISC), Sep. 2014, pp. 15–20.

Z. U. Khan and M. Benaissa, “High-speed and low-latency ECC processor implementation over GF(2m) on FPGA,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 25, no. 1, pp. 165–176, Jan. 2017.

R. Salarifard, S. Bayat-Sarmadi and H. Mosanaei-Boorani, "A Low-Latency and Low-Complexity Point-Multiplication in ECC," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 9, pp. 2869-2877, Sept. 2018, doi: 10.1109/TCSI.2018.2801118.