Design and Analysis of High Speed Multiply and Accumulation Unit for Digital Signal Processing Applications

Main Article Content

Abstract

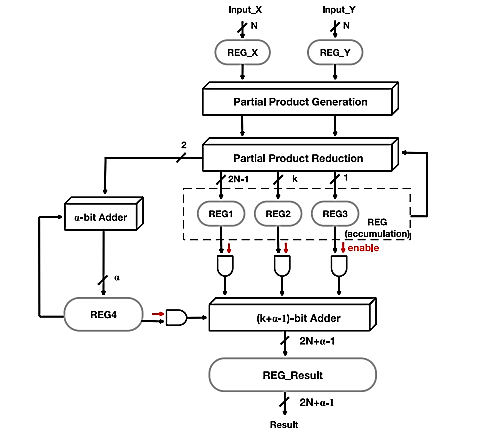

The fundamental component used in many of the Digital signal Processing (DSP) applications are Multiply and Accumulation Unit (MAC). In the literature, a multiplier consists of greater number of full adders and half adder in partial product reduction stage, which increases the hardware complexity and critical path delay to MAC unit. To overcome this problem, two novel multipliers are proposed in this article. The proposed multipliers are designed and implemented in hardware, which reduces the circuit complexity and improves the overall performance of the MAC unit with less delay. The proposed multipliers are compared with the 4-bit existing designs and observed that the number of slices Look Up Tables (LUTs) are minimized from 113 to 43, Slices are reduced from 46 to 14, Full Adders (FAs) are lessened from 28 to 23, bonded Input Output Blocks (IOBs) and Half Adders (HAs) were not altered. The time delay is reduced from 14.251ns to 7.876ns. The proposed multipliers are compared in the literature with the 8-bit multiplier, then the number of Slice LUTs are reduced from 510 to 231, Slices are reduced from 218 to 113, FAs are reduced from 120 to 110, HAs are reduced from 56 to 39, time delay is reduced from 26.228ns to12.748ns, but bonded IOBs count remains same. The synthesis and simulations results are verified by using Xilinx ISE 14.7 version tool.

Article Details

References

M. Basavoju Harish, “Design of MAC unit for digital filters in signal processing and communication,” in International Journal of Speech Technology.

N. Bhuvaneswary ,‘‘Efficient Implementation of Multiply Accumulate Operation Unit Using an Interlaced Partition Multiplier’’ in Journal of Computational and Theoretical Nanoscience, Volume 18, Number 4, April 2021, pp. 1321-1326(6).

Jayakumar, “Vedic Arithmetic Based High Speed & Less Area MAC Unit for Computing Devices”, in Recent Advances in Computer Science and Communications (Formerly: Recent Patents on Computer Science), Volume 13, Number 6, 2020, pp. 1079-1082(4).

Hao Zhang, “New Flexible Multiple-Precision Multiply-Accumulate Unit for Deep Neural Network Training and Inference”, in , IEEE Transactions on Computers.

Jongsung Kang, “PV-MAC: Multiply-and-accumulate unit structure exploiting precision variability in on-device convolutional neural networks”, in the VLSI Journal.

M. Janani Preeyaa, “MULTICHANNEL MAC UNIT FOR DSP APPLICATIONS”, in International Research Journal of Modernization in Engineering Technology and Science Volume:03/Issue:05/May-2021.

K. Rashmi, “IMPLEMENTATION OF LOW POWER, HIGH SPEED MAC UNIT”, in International Research Journal of Modernization in Engineering Technology and Science Volume:03/Issue:05/May-2021.

S.China Venkateswarlu, “Implementation of Area optimized Low power Multiplication and Accumulation”, in International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-9, Issue-1, November 2019.

G. Indira, “Design and implementation of Multiplier Accumulator (MAC) unit using Rounding Based Approximate (RoBA)”, in Journal of Information and Computational Science Volume 10 Issue 9 - 2020 ISSN: 1548-7741

Gopi Chand Naguboina, “Implementation of MAC Unit using Modified IEEE – 754 Floating Point Multiplier with Enhanced Speed”, in Mukt Shabd Journal Volume IX, Issue VI, JUNE/2020 ISSN NO : 2347-3150

S N. Manoj Kumar, “An Efficient Design of 16 Bit MAC Unit using Vedic Mathematics”, in BOHR International Journal of Intelligent Instrumentation and Computing 2021, Vol. 1, No. 1, pp. 1–4

C Vincent Camus, “Review and Benchmarking of Precision-Scalable Multiply-Accumulate Unit Architectures for Embedded Neural-Network Processing”, in IEEE JOURNAL ON EMERGING AND SELECTED TOPICS IN CIRCUITS AND SYSTEMS, VOL. 9, NO. 4,.

C R. Suguna, “Hybrid spectrum sensing architecture using LLCBC MAC for CR-WSN applications”, in Analog Integrated Circuits and Signal Processing .

JM.V.S.Ramprasad, “Design of High Speed and Area Efficient 16 Bit MAC Architecture Using Hybrid Adders for Sustainable Application”, in Journal of Green Engineering (JGE) Volume-10, Issue-11.

T. T. Hoang, M. Sjalander, and P. Larsson-Edefors, ‘‘A high-speed, energy- ef?cient two-cycle multiply-accumulate (MAC) architecture and its appli- cation to a double-throughput MAC unit,’’ IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 12, pp. 3073–3081, Dec. 2010.

P. Jebashini, R. Uma, P. Dhavachelv, and H. K. Wye, ‘‘A survey and comparative analysis of multiply-accumulate (MAC) block for digital signal processing application on ASIC and FPGA,’’ J. Appl. Sci., vol. 15, no. 7, pp. 934–946, Jul. 2015.

A. Wahba and H. Fahmy, ‘‘Area ef?cient and fast combined Binary/Decimal ?oating point fused multiply add unit,’’ IEEE Trans. Comput., vol. 66, no. 2, pp. 226–239, Feb. 2017.

C. P. Narendra and K. M. R. Kumar, ‘‘Low power compressor based MAC architecture for DSP applications,’’ in Proc. IEEE International Conference in Signal Processing Information Communication Energy Systems (SPICES), Kozhikode, India, Feb. 2015, pp. 1–5.

che-win ting, Shih-hsu huang,” A High-Performance Multiply-Accumulate Unit by Integrating Additions and Accumulations Into Partial Product Reduction Process” volume 8, 2020.

Corey Lammie, “ Memristive Stochastic Computing for Deep Learning Parameter Optimization”, in by Ieee Transactions On Circuits And Systems Part Ii: Express Briefs, 2021.

Ahammad, S.H.,Rajesh, V. Venkatesh, K.N., ... Rao, P.R. Inthiyaz, S., “Liver segmentation using abdominal CT scanning to detect liver disease area”, International Journal of Emerging Trends in Engineering Research, 2019, 7(11), pp. 664–669, 41.

Murali Krishna, B.,Siva Kumar, M., Rajesh, J., ...Bhavani, M., Adidela, C.N., “FPGA implementation by using XBee transceiver”, Indian Journal of Science and Technology, 2016, 9(17), 93032.

Inthiyaz, S., Tulasi, S.K., Jayanthi, R.S.L., Sahitya, C., Jyothi, C., “Design of bi-trigger sram using schmitt trigger for low power 13t cmos application”, International Journal of Scientific and Technology Research, 2019, 8(12), pp. 1466–1471.

Siva Kumar, M., Inthiyaz, S., Dhamini, J., Sanjay, A., Chandu Srinivas, U., “Delay estimation of different approximate adders using mentor graphics”, International Journal of Advanced Trends in Computer Science and Engineering, 2019, 8(6), pp. 3584–3587.

Inthiyaz, S., Madhav, B.T.P., Kishore Kumar, P.V.V., ...Srikanth, K., Arun Teja, B., “Flower image segmentation: A comparison between watershed, marker controlled watershed, and watershed edge wavelet fusion”, ARPN Journal of Engineering and Applied Sciences, 2016, 11(15), pp. 9382–9387

Myla, S., Marella, S.T., Swarnendra Goud, A., Hasane Ahammad, S., Kumar, G.N.S., Inthiyaz, S., “Design decision taking system for student career selection for accurate academic system”, International Journal of Recent Technology and Engineering, 8(9), pp. 2199-2206.

Srinivasa Reddy, K., Suneela, B., Inthiyaz, S., Hasane Ahammad, S., Kumar, G.N.S., Mallikarjuna Reddy, A., “Texture filtration module under stabilization via random forest optimization methodology”, International Journal of Advanced Trends in Computer Science and Engineering, 8(3), pp. 458-469.

Poorna Chander Reddy, A., Siva Kumar, M., Murali Krishna, B., Inthiyaz, S., Ahammad, S.H., “Physical unclonable function based design for customized digital logic circuit”, International Journal of Advanced Science and Technology, 28(8), pp. 206-221.

Nagageetha, M., Mamilla, S.K., Hasane Ahammad, S., “Performance analysis of feedback based error control coding algorithm for video transmission on wireless multimedia networks”, Journal of Advanced Research in Dynamical and Control Systems, 9(Special Issue 14), pp. 626-660.