Design of Hybrid Full Adder using 6T-XOR-Cell for High Speed Processor Designs Applications

Main Article Content

Abstract

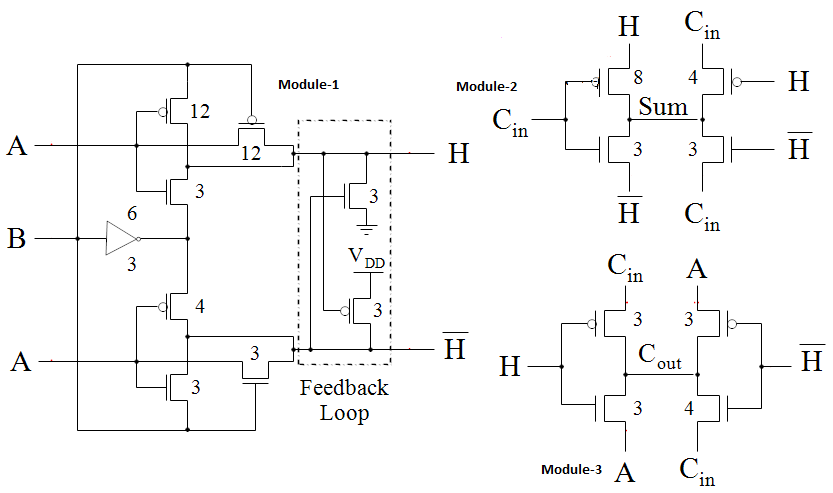

Hybrid-logic implementation is highly suitable in the design of a full adder circuit to attain high-speed low-power consumption, which helps to design n any high speed ALUs that can be used in varies processors and applicable for high speed IoT- Application. XOR/XNOR-cell, Hybrid Full Adder (HFA) are the fundamental building block to perform any arithmetic operation. In this paper, different types of high-speed, low-power 6T-XOR/XNOR-cell designs are being proposed and simulated results are presented. The proposed HFA is simulated using a cadence virtuoso environment in a 45nm technology with supply voltage as 0.8V at 1GHz. The proposed HFA consumes a power of 1.555uw, and the delay is 36.692ns. Layout designs are drawn for both 6T-XOR/XNOR-cell, and 1- bit HFA designs. XOR/XNOR-cells are designed based on the combination of normal CMOS-inverter and Pass Transistor Logic (PTL). Which is used in the design of high end device processors such as ALU that can be implemented for the IoT- design applications?

Article Details

References

Jyoti Kandpal, Abhishek Tomar, Mayur Agarwal, and K. K. Sharma (2020) -" High-Speed Hybrid-Logic Full Adder Using High-Performance 10-T XOR–XNOR Cell-IEEE IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 28(6), pp-1413-1422.

Mehedi Hasan, Md. Jobayer Hossein, Mainul Hossain, Hasan U. Zaman, and SharnaliIslam (2020)-" Design of a Scalable Low-Power 1-Bit Hybrid Full Adder for Fast Computation"- IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 67(8), pp-1464-1468, .

Hareesh-Reddy Basireddy, Karthikeya Challa, and Tooraj Nikoubin-“ Hybrid Logical Effort for Hybrid Logic Style Full Adders in Multistage Structures” (2019) - IEEE Trans. Very Large Scale Integr. (VLSI) Syst., Vol. 27(5), pp-1138-1147.

K. Haghshenas, M. Hashemi, and T. Nikoubin, (2018) "Fast and energy-efficient CNFET adders with CDM and sensitivity-based device-circuit co-optimization," IEEETrans.Nanotechnol.,vol.17(4), pp.783–794,

T. Nikoubin, M. Grailoo, and C. Li,(2016) "Energy and area-efficient three-input XOR-CELLs with systematic cell design methodology,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 24(1), pp. 398–402.

Shubhajit Roy Chowdhury, Aritra Banerjee, Aniruddha Roy, Hiranmay Saha (2008) –“A high Speed 8 Transistor Full Adder Design Using Novel 3 Transistor XOR Gates International Journal of Electronics and Communication EngineeringVol: 2(10),

R. M. Anacan and J. L. Bagay, (2015)“Logical effort analysis of various VLSI design algorithms,” in Proc. IEEE Int. Conf. Control Syst., Comput. Eng. (ICCSCE), George Town, Malaysia, pp.19–23.

P. Pramod & T. K. Shahana-" Delay and Energy Efficient Modular Hybrid Adderfor Signal Processor Architectures"- IETE Journal of Research.

Partha Bhattacharyya, Bijoy Kundu, Sovan Ghosh, Vinay Kumar, and Anup Dandapat (2015)“ Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit- IEEE Trans. Very Large Scale Integr. (VLSI) Syst, 23(10) pp-2001-2008.

Sameer Goel, Ashok Kumar, and Magdy A. Bayoumi, Fellow, IEEE-“ Design of Robust, Energy-Efficient Full Adders for Deep- Submicrometer Design UsingHybrid-CMOS Logic Style- IEEE Trans. Very Large Scale Integr. (VLSI) Syst, VOL. 14(2) ,2008.

Venkat Subba Rao.Manchala,Ramana Murthy.Gajula "Low-Power and Low-Leakage Design Techniques in CMOS T echnology" Proceedings of the Fifth International Conference on Trends in Electronics and Informatics (ICOEI). IEEE Xplore Part Number:CFP21J32-ART; ISBN:978-1-6654-1571-2

Venkat Subbarao.Manchal,Satyajeet Sahoo, G.Ramana Murthy."Design and analysis of 16- bit spares kogge stone adder with proposed 6T-XOR cell, 1- bit HFA design for high speed Arithmetic operations".2022 International Conference on Communication, Computing and Internet of Things (IC3IoT) | 978-1-6654-7995-DOI: 10.1109/IC3IOT53935.2022.9767976.

Venkat Subbarao.Manchal,Satyajeet Sahoo, G.Ramana Murthy."Design and analysis of Novel XOR/XNOR Based Hybrid Full Adder for IoT- Applications 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021) -978-1-6654-6633- IEEE DOI: 10.1109/ICRTCST54752.2022.97819. Sahoo, S. and Prabaharan, S.R., 2017. Nano-ionic solid state resistive memories (re-RAM): A review. Journal of nanoscience and nanotechnology, 17(1), pp.72-86.DOI-10.1166/jnn.2017.12805.

Sahoo, S., Manoravi, P. and Prabaharan, S.R.S., 2019. Titania Based Nano-ionic Memristive Crossbar Arrays: Fabrication and Resistive Switching Characteristics. Nanoscience & Nanotechnology-Asia, 9(4), pp.486-493.DOI:https://doi.org/10.2174/2210681208666180628122146.

Sahoo, S., 2021. Conduction and switching behavior of e-beam deposited polycrystalline Nb2O5 based nano-ionic memristor for non-volatile memory applications. Journal of Alloys and Compounds, 866,p.158394.DOIhttps://doi.org/10.1016/j.jallcom.2020.158394

Masoud Pashaeifar, Mehdi Kamal, Ali Afzali-Kusha, and Massoud Pedram(2018)“Approximate Reverse Carry Propagate Adder for Energy-Efficient DSP Applications”- IEEE Trans. Very Large Scale Integr. (VLSI) Syst, 26(11), pp-2530-254,

Sana pala, Ramachandran Sakthivel,(2019) "Ultra-low-voltage GDI-based hybrid full adder design for the area and energy-efficient systems"-IET Circuits, Devices & Systems, Vol. 13 (4) pp. 465-470

K.Navi, V.Foroutan, M.RahimiAzghadi, M.Maeen, M.Ebrahimpour, M.Kaveh, O.Kavehei (2009)" A novel low-power full-adder cell with a new technique in designing logical gates based on static CMOS inverter-Microelectronics Journal 40 (2009), pp-1441-1448

H. Naseri and S. Trimarchi,(2018) “Low-power and fast full adder by exploring new XOR and XNOR gates,” IEEE Trans. Very Large Scale. Integer. (VLSI) Syst., vol. 26(8), pp. 1481–1493, Aug.2018.

M. Amini-Valashani, M. Ayat, and S. Mirzakuchaki, "Design and analysis of a novel low-power and energy-efficient 18T hybrid full adder,” Microelectron. J., vol. 74, pp. 49–59, Apr.2018.

M. A. Valashani and S. Mirzakuchaki (2016), “A novel fast, low-power and high-performance XOR-XNOR cell,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2016, pp.694–697.

M. J. Zavarei, M. R. Baghbanmanesh, E. Kargaran, H.Nabovati, and A. Golmakani,(2011) “Design of new full adder cell using hybrid-CMOS logic style,” inProc.18thIEEEInt.Conf.Electron.,Circuits, Syst., Dec.2011, pp.451–454

C.-H. Chang, J. Gu, and M. Zhang (2005) “A review of 0.18-µm full adder performances for tree-structured arithmetic circuits,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 6, pp. 686–695.

A.P. Chandrakasan, S.Sheng,andR.W.Brodersen,(1992) "Low-power CMOS digital design,” IEICE Trans. Electron., vol. 75(4), pp. 371–382, 1992.

R. Zimmermann and W. Fichtner(1997) “Low-power logic styles: CMOS versus pass-transistor logic,” IEEE J. Solid-State Circuits, vol. 32, no. 7, pp. 1079–1090, Jul.1997.

M. Aguirre-Hernandez and M. Linares-Aranda,(2011) “CMOS full-adders for energy-efficient arithmetic applications,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 4, pp. 718–721.

V. Foroutan, M. Taheri, K. Navi, and A. A. Mazreah,(2014) “Design of two low-power full adder cells using GDI structure and hybrid CMOS logic style,” Integration, vol. 47, no. 1, pp. 48–61.

M. Agarwal, N. Agrawal, and M. A. Alam (2014) “A new design of low-power high-speed hybrid CMOS full adder,” in Proc. Int. Conf. Signal Process. Integer. Netw. (SPIN), pp.448–452.

M. Vesterbacka(1999) “A 14-transistor CMOS full adder with full voltage- swing nodes,” in Proc. IEEE Workshop Signal Process. Systems. Design Implement. (SiPS), pp.713–722.

H. Tien Bui, Y. Wang, and Y. Jiang(2002) “Design and analysis of low-power 10-transistor full adders using novel XOR-XNOR gates,” IEEE Trans. CircuitsSyst.II, AnalogDigit.SignalProcess.,vol.49(1),pp.25–30, 2002.

M. Zhang, J. Gu, and C.-H. Chang (2003) “A novel hybrid pass logic with static CMOS output drive full-adder cell,” in Proc. Int. Symp. Circuits Syst. (ISCAS),vol.5,May2003,p.5.

P. Malini G. Naveen Balaji K. Boopathiraja (2019)-“Design of Swing Dependent XOR-XNOR Gates based Hybrid Full Adder”- 2019 5th International Conference on Advanced Computing & Communication Systems (ICACCS)-pp-1164-1170

A.P. Chandrakasan, S.Sheng,andR.W.Brodersen (1992) "Low-power CMOS digital design,” IEICE Trans. Electron., vol. 75, no. 4, pp. 371–382, 1992.

D. Radhakrishnan,(2001)“Low-voltage low-power CMOS full adder,” IEE Proc.-Circuits, Devices Syst., vol. 148, no. 1, pp. 19–24, Feb. 2001.

M.Geetha Priya1, Dr.K.Baskaran2, D.Krishnaveni,(2012)- Leakage Power Reduction Techniques in Deep Submicron Technologies for VLSI Applications- International Conference on Communication Technology and System Design 2011- Elsevier-Procedia Engineering pp: 1163 – 1170.

Bagyalakshmi K, M. Karpagam(2020).- "Performance enhancement of efficient process based on Carry-Skip Adder for IoT applications"- Microprocessors and Microsystems- Elsevier -Contents lists available at Science.

Manan Mewada, Mazad Zaveri, Rajesh Thakker (2019)."Improving the performance of transmission gate and hybrid CMOS Full Adders in a chain and tree structure architectures"- Elsevier-Integration, the VLSIJournal-0167-9260/2019- Elsevier.

MajidAmini-Valashani, MehdiAyat, SattarMirzakuchaki (2018) "Design and Analysis of a Novel Low power and energy -Efficient 18T Hybrid Full adder" - Micro Electronics Journal- Elsevier Volume-74(5), Pages 49-59.

Salam Surjit Singh, Dolly Leishangthem, Md. Nasiruddin Shah ,Biraj Shougaijam. "A Unique Design of Hybrid Full Adder for the Application of Low Power VLSI Circuits".Fourth International Conference on Electronics, Communication and Aerospace Technology (ICECA-2020) IEEE Xplore Part Number: CFP20J88-ART; ISBN: 978-1-7281-6387-1.

Sahoo, S., 2021. Conduction and switching behavior of e-beam deposited polycrystalline Nb2O5 based nano-ionic memristor for non-volatile memory applications. Journal of Alloys and Compounds, 866,p.158394.DOIhttps://doi.org/10.1016/j.jallcom.2020.158394.