Design and Implementation of Hybrid Multiplier for DSP Applications

Main Article Content

Abstract

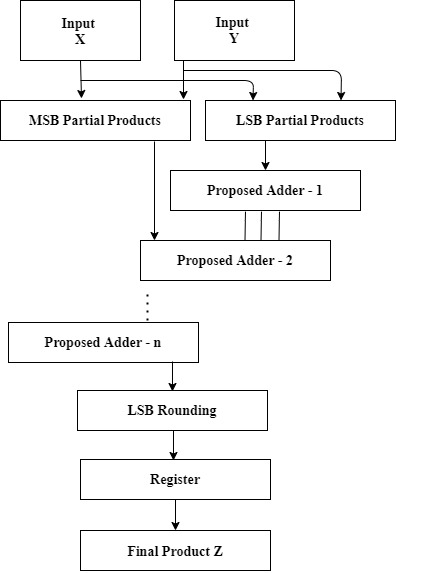

In recent decades, there has been a consistent reduction in feature sizes in integrated circuit (IC) technology, leading to the need for increased placement of functional circuits on each chip. When it comes to the design of digital circuits, there is a significant focus on hybrid logic. Hybrid logic is highly regarded due to its ability to consume less power while achieving higher efficiency. Hybrid logic circuits have similarities to complementary metal-oxide-semiconductor (CMOS) transistors, yet possess a reduced transistor count while offering enhanced performance and reliability capabilities. This study examines the modeling and implementation hybrid multiplier with of help of hybrid adder. The functionality of adder is determined with the help of hybrid logic producing XOR/XNOR functionalities in single circuit. The proposed hybrid Multiplier, which incorporates a hybrid Adder, has been successfully designed and implemented using CMOS 45nm technology and Mentor Graphics software the hybrid transistor logic multiplier demonstrates a decrease in total delay of 60% compared to CMOS.