Expanded Noise Margin 10T SRAM Cell using Finfet Device

Main Article Content

Abstract

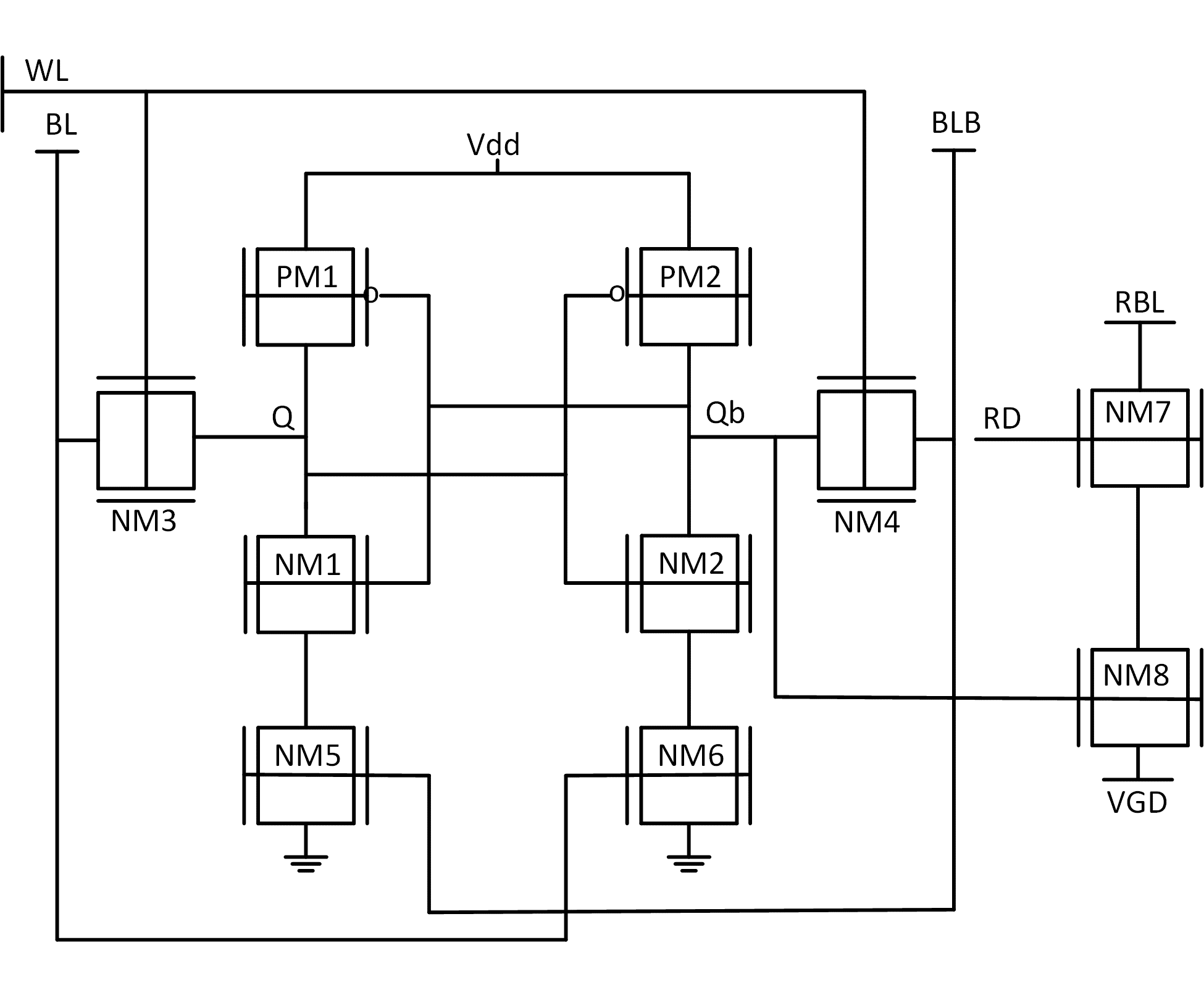

Static random access memory (SRAM) cells are being improved in order to increase resistance to device level changes and satisfy the requirements of low-power applications. A unique 10-transistor FinFET-based SRAM cell with single-ended read and differential write functionality is presented in this study. This cutting-edge architecture is more power-efficient than ST (Schmitt trigger) 10T or traditional 6T SRAM cells, using only 1.87 and 1.6 units of power respectively during read operations. The efficiency is attributable to a lower read activity factor, which saves electricity. The read static noise margin (RSNM) and write static noise margin (WSNM) of the proposed 10T SRAM cell show notable improvements over the 6T SRAM cell, increasing by 1.67 and 1.86, respectively. Additionally, compared to the 6T SRAM cell, the read access time has been significantly reduced by 1.96 seconds. Utilising the Cadence Virtuoso tool and an 18nm Advanced Node Process Design Kit (PDK) technology file, the design's efficacy has been confirmed. For low-power electronic systems and next-generation memory applications, this exciting 10T SRAM cell has a lot of potential.

Article Details

References

Frank, D.J., Dennard, R, H., Nowak, E., Solomon, P.M., Taur, Y., & Wong, H.S.P. (2001). Device Scaling Limits of Si MOSFETs and Their Application Dependencies. Proceedings of the IEEE, 89(3), p.259-288.

Farkhani, H., Peiravi, A., Kargaard, J.M. & Moradi, F. (2014). Comparative Study of FinFETs versus 22nm Bulk CMOS Technologies : SRAM Design Perspective. 27th IEEE International System-On-Chip Conference, p. 449-454.

King, T.J. (2005). FinFETs for Nanoscale CMOS Digital Integrated Circuits. IEEE/ACM International Conference on Computer-Aided Design, p. 207-210.

Jain, P.U., & Tomar, V.K. (2020). FinFET TECHNOLOGY : As A Promising Alternatives for

Conventional MOSFET Technology. IEEE International Conference on Emerging Smart Computing and Informatics, p. 43-47.

Gore Santosh, Dutt, I. ., Dahake, R. P. ., Khodke, H. E. ., Kurkute, S. L. ., Dange, B. J. . and Gore, Sujata (2023) “Innovations in Smart City Water Supply Systems ”, International Journal of Intelligent Systems and Applications in Engineering, 11(9s), pp. 277–281. Available at: https://ijisae.org/index.php/IJISAE/article/view/3118.

Nayak, D., Acharya, D.P., Rout, P.K., & Nanda, U. (2018). A High Stable 8T-SRAM with Bit Inter-leaving capability for Minimization of Soft Error Rate. Microelectronics Journal, 73, p.43-51.

Verma, J., Passi, A., Sindhu, S., & Gayathiri, S. (2019). Design 10-Transistor (10T) SRAM Using FinFET Technology. International Journal of Engineering and Advance Technology, 9(1), p.566-572.

Sachdeva, A., & Tomar, V.K. (2021). Design of 10-T SRAM Cell with Improved Read Performance and Expended Write Margin. IET Journal of Circuits, Devices, and Systems, 15(1), p. 42-64.

Tayade, V.P., & Lahudkar, S.L. (2022). Implementation of 20 nm Graphene Channel Field-Effect Transistors Using Silvaco TCAD Tool to Improve Short Channel Effects over Conventional MOSFETs. Advances in Technology Innovation, 7(1), p.19-29.

Ensan, S.S., Moaiyeri, M.H., Moghaddam, M., & Hessabi, S. (2019). A Low-Power Single-Ended SRAM in FinFET Technology. International Journal of Electronics and Communications, 99, p.361-368.

Yang, Y., Park, J., Song, S.C., Wang, J., Yeap, G., & Jung, S.O. (2015). Single-Ended 9T SRAM Cell for Near-Threshold Voltage Operation with Enhanced Read Performance in 22-nm FinFET Technology. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23(11), p.2748-2752.

Chang, J., Chen, Y., Chan, W., Singh, S. P., Cheng, H., Fujiwara, H., Lin, J.-Y. Lin, K.C., Hung, J., Lee, R., Liao, H.J., Liaw, J.J., Li, Q., Lin, C.Y., Chiang, M.C., & Wu, S.Y. (2017). 12.1 A 7nm 256Mb SRAM in High-k Metal-Gate FinFET Technology with Write-Assist Circuitry for Low-VMIN Applications. IEEE International Solid-State Circuits Conference, p. 206-207.

Guler, A., & Jha, N.K. (2019). Three-Dimensional Monolithic FinFET-Based 8T SRAM Cell Design for Enhanced Read Time and Low Leakage. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 27(04), p.899-912.

Dange, B. J ., Mishra, P. K ., Metre, K. V., Gore Santosh, Kurkute, S. L., Khodke, H. E. and Gore Sujata (2023) “Grape Vision: A CNN-Based System for Yield Component Analysis of Grape Clusters ”, International Journal of Intelligent Systems and Applications in Engineering, 11(9s), pp. 239–244. Available at: https://ijisae.org/index.php/IJISAE/article/view/3113.

Ramakrishnan, V.N., & Srinivasan, R. (2012). Soft Error Study in Double-Gated FinFET-Based SRAM Cells with Simultaneous and Independent Driven Gates. Microelectronics Journal, 43(11), p. 888-893.

Zeinali, B., Madsen J.K., Raghavan, P., & Moradi, F. (2017). Low-Leakage Sub-threshold 9T-SRAM cell in 14-nm FinFET Technology. International Journal of Circuit Theory and Applications, 45(11), p. 1647-1659.

Turi, M. A., & Delgado-Frias, J.G. (2017). Full-Vdd and Near-Threshold Performance of 8T FinFET SRAM Cells. Integration, 57, p.169-183.

Kulkarni, J.P., Kim, K., & Roy, K. (2007). A 160 mV Robust Schmitt Trigger Based Sub-threshold SRAM. IEEE Journal of Solid-State Circuits, 42(10), p. 2303-2313.

Karamimanesh, M., Abiri, E., Hassanli, K., Salehi M.R., & Darabi, A. (2021). A Robust and Write Bit-line Free Sub-threshold 12T-SRAM for Ultra-Low Power Applications in 14nm FinFET Technology. Microelectronics Journal, 118, p. 105185.

Sachdeva, A., & Tomar, V.K. (2021). Design of Low Power Half Select Free 10-T Static Random Access Memory cell. Journal of Circuits, Systems, and Computers, 30(04), p. 2150073.

Tholkapiyan, M. ., Ramadass, S. ., Seetha, J. ., Ravuri, A. ., Vidyullatha, P. ., Shankar S., , S. . and Gore, S. . (2023) “Examining the Impacts of Climate Variability on Agricultural Phenology: A Comprehensive Approach Integrating Geoinformatics, Satellite Agrometeorology, and Artificial Intelligence”, International Journal of Intelligent Systems and Applications in Engineering, 11(6s), pp. 592–598. Available at: https://ijisae.org/index.php/IJISAE/article/view/2891.

Zhou, J., Jayapal, S., Ben, B., Li, H., & Stuyt, J. (2011). A 40 nm inverse-narrow-width-effect-aware sub-threshold standard cell library. Proceedings of the 48th Design Automation Conference, p. 441-446

Pavlov A., & Sachdev M. (2008). CMOS SRAM Circuit Design and Parametric Test in Nano-Scaled Technologies : Process-Aware SRAM Design and Test. Springer Science & Business Media, p. 1–180.

Tomar, V.K., & Sachdeva, A. (2022). Design of A Soft Error Hardened SRAM Cell with Improved Access Time for Embedded Systems. Microprocessors and Microsystems, 90,104445.

Chatterjee, I., Narasimham, B., Mahatme, N. N., Bhuva, B. L., Reed, R. A., Schrimpf, R. D., Wang, J. K., Vedula, N., Bartz, B., & Monzel, C. (2014). Impact of Technology Scaling on SRAM Soft Error Rates. IEEE Transactions on Nuclear Science, 61(6), p.3512-3518.