Design and Develop Efficient Arbitration Technique to Handle the Multiple Refresh Requests in Multi-Processor SoC

Main Article Content

Abstract

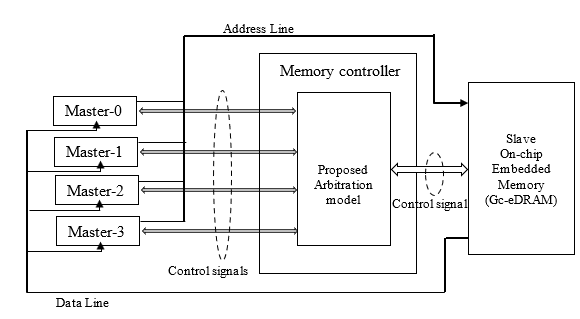

Emerging memory technologies, such as Gain Cell-embedded Dynamic Random Access Memory (GC-eDRAM), play an essential part in the process of improving the overall performance of current multi-processor systems. GC-eDRAM, on the other hand, has its own set of distinct issues, particularly with regard to refresh operations. The number of cores and threads in contemporary processors continues to expand, which in turn leads to an increase in the number of concurrent refresh requests. This might cause contention, which in turn can lead to a possible performance decrease. In this article, we present an efficient arbitration method that was developed in order to precisely address the issues that are associated with numerous requests for a refresh in GC-eDRAM. This method takes use of the inherent parallelism of GC-eDRAM modules to make it possible to execute simultaneous refresh operations. As a result, contention is effectively reduced, and the overall performance of the system is improved. We provide a new arbitration method that prioritizes the pending refresh requests according to their level of urgency and optimizes the allocation of GC-eDRAM resources in order to guarantee that refresh operations are carried out in an effective manner. Our method modifies the arbitration priority in a dynamic manner according to the characteristics of the active workload. These characteristics include the request arrival rate, memory access patterns, and data location, among other considerations.

Article Details

References

. Hoffmann, Henry, Axel Jantsch, and Nikil D. Dutt. "Embodied self-aware computing systems." Proceedings of the IEEE 108, no. 7 (2020): 1027-1046.

. Uma, V., and Ramalatha Marimuthu. "D-wash–A dynamic workload aware adaptive cache coherance protocol for multi-core processor system." Microelectronics Journal 132 (2023): 105675.

. Goel, Tanmay, Divyansh Maura, Kaustav Goswami, Shirshendu Das, and Dip Sankar Banerjee. "Towards row sensitive DRAM refresh through retention awareness." In 2021 22nd International Symposium on Quality Electronic Design (ISQED), pp. 450-456. IEEE, 2021.

. Yang, Jia?Qin, Ye Zhou, and Su?Ting Han. "Functional applications of future data storage devices." Advanced Electronic Materials 7, no. 5 (2021): 2001181.

. Brand, Marcel, Michael Witterauf, Éricles Sousa, Alexandru Tanase, Frank Hannig, and Jürgen Teich. "*?Predictable MPSoC execution of real?time control applications using invasive computing." Concurrency and Computation: Practice and Experience 33, no. 14 (2021): e5149.

. Suresh, K. S. ., & Kamalakannan, T. . (2023). Digital Image Steganography in the Spatial Domain Using Block-Chain Technology to Provide Double-Layered Protection to Confidential Data Without Transferring the Stego-Object. International Journal of Intelligent Systems and Applications in Engineering, 11(2s), 61–68. Retrieved from https://ijisae.org/index.php/IJISAE/article/view/2508

. Garzón, Esteban, Yosi Greenblatt, Odem Harel, Marco Lanuzza, and Adam Teman. "Gain-cell embedded DRAM under cryogenic operation—A first study." IEEE Transactions on Very Large-Scale Integration (VLSI) Systems 29, no. 7 (2021): 1319-1324.

. Shrivastava, Anurag, and Sudhir Kumar Sharma. "Various arbitration algorithm for on-chip (AMBA) shared bus multi-processor SoC." In 2016 IEEE Students' Conference on Electrical, Electronics and Computer Science (SCEECS), pp. 1-7. IEEE, 2016.

. Noy, Tzachi, and Adam Teman. "Design of a refresh-controller for GC-eDRAM based FIFOs." IEEE Transactions on Circuits and Systems I: Regular Papers 67, no. 12 (2020): 4804-4817.

. Narinx, Jonathan, Robert Giterman, Andrea Bonetti, Nicolas Frigerio, Cosimo Aprile, Andreas Burg, and Yusuf Leblebici. "A 24 kb single-well mixed 3T gain-cell eDRAM with body-bias in 28 nm FD-SOI for refresh-free DSP applications." In 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 219-222. IEEE, 2019.

. Widmer, Marco, Andrea Bonetti, and Andreas Burg. "FPGA-based emulation of embedded DRAMs for statistical error resilience evaluation of approximate computing systems." In Proceedings of the 56th Annual Design Automation Conference 2019, pp. 1-6. 2019.

. Seyedzadeh Sany, Bahareh, and Behzad Ebrahimi. "A 1?GHz GC?eDRAM in 7?nm FinFET with static retention time at 700 mV for ultra?low power on?chip memory applications." International Journal of Circuit Theory and Applications 50, no. 2 (2022): 417-426.

. Lee, Changmin, Wonjae Shin, Dae Jeong Kim, Yongjun Yu, Sung-Joon Kim, Taekyeong Ko, Deokho Seo et al. "Nvdimm-c: A byte-addressable non-volatile memory module for compatibility with standard ddr memory interfaces." In 2020 IEEE International Symposium on High Performance Computer Architecture (HPCA), pp. 502-514. IEEE, 2020.

. Cui, Jinhua, Youtao Zhang, Liang Shi, Chun Jason Xue, Jun Yang, Weiguang Liu, and Laurence T. Yang. "Leveraging partial-refresh for performance and lifetime improvement of 3D NAND flash memory in cyber-physical systems." Journal of Systems Architecture 103 (2020): 101685.

. Brian Moore, Peter Thomas, Giovanni Rossi, Anna Kowalska, Manuel López. Machine Learning for Fraud Detection and Decision Making in Financial Systems. Kuwait Journal of Machine Learning, 2(4). Retrieved from http://kuwaitjournals.com/index.php/kjml/article/view/216

. Steiner, Lukas, Matthias Jung, Felipe S. Prado, Kirill Bykov, and Norbert Wehn. "DRAMSys4. 0: a fast and cycle-accurate systemC/TLM-based DRAM simulator." In Embedded Computer Systems: Architectures, Modeling, and Simulation: 20th International Conference, SAMOS 2020, Samos, Greece, July 5–9, 2020, Proceedings 20, pp. 110-126. Springer International Publishing, 2020.