Design of Digital Frequency Synthesizer for 5G SDR Systems

Main Article Content

Abstract

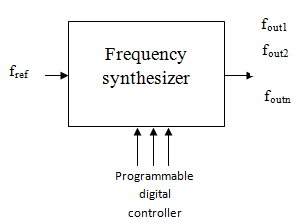

The previous frequency synthesizer techniques for scalable SDR are not compatible with high end applications due to its complex computations and the intolerance over increased path interference rate which leads to an unsatisfied performance with improved user rate in real time environment. Designing an efficient frequency synthesizer framework in the SDR system is essential for 5G wireless communication systems with improved Quality of service (QoS). Consequently, this research has been performed based on the merits of fully digitalized frequency synthesizer and its explosion in wide range of frequency band generations. In this paper hardware optimized reconfigurable digital base band processing and frequency synthesizer model is proposed without making any design complexity trade-off to deal with the multiple standards. Here fully digitalized frequency synthesizer is introduced using simplified delay units to reduce the design complexity. Experimental results and comparative analyzes are carried out to validate the performance metrics and exhaustive test bench simulation is also carried out to verify the functionality.

Article Details

References

Kumar, B. P., & Paidimarry, C. S. (2020). Improved real time GPS RF data capturing for GNSS SDR applications. Gyroscopy and Navigation, 11(1), 59-67.

Petrov, A. A., Davydov, V. V., & Grebennikova, N. M. (2018). On the potential application of direct digital synthesis in the development of frequency synthesizers for quantum frequency standards. Journal of Communications Technology and Electronics, 63(11), 1281-1285.

Mortezapour, Siamak, and Edward KF Lee. "Design of low-power ROM-less direct digital frequency synthesizer using nonlinear digital-to-analog converter." IEEE Journal of Solid-state circuits 34.10 (1999): 1350-1359.

Haas, Sebastian, et al. "A heterogeneous SDR MPSoC in 28 nm CMOS for low-latency wireless applications." Proceedings of the 54th Annual Design Automation Conference 2017. 2017.

Hatami, Safar, et al. "Single-bit pseudoparallel processing low-oversampling delta–sigma modulator suitable for SDR wireless transmitters." IEEE Transactions on Very Large Scale Integration (VLSI) Systems 22.4 (2013): 922-931

Inguva, S. C., & Seventiline, J. B. (2019). LH-CORDIC: Low power FPGA based implementation of CORDIC architecture. International Journal of Intelligent Engineering and Systems, 12(2), 305-314.

Yan, B., Pan, C., Beck, T., Jin, X., Wang, L., Liang, D., ... & Hao, W. (2022). New Reprocessing towards Life-Time Quality-Consistent Suomi NPP OMPS Nadir Sensor Data Records (SDR): Calibration Improvements and Impact Assessments on Long-Term Quality Stability of OMPS SDR Data Sets. Remote Sensing, 14(13), 3125.

Garcia .E.O., et al (2006), “Pipelined CORDIC design on FPGA for a digital sine and cosine waves generator”, In 2006 3rd International Conference on Electrical and Electronics Engineering, pp. 1-4. IEEE.

Genovese, Mariangela, et al. "Analysis and comparison of Direct Digital Frequency Synthesizers implemented on FPGA." Integration 47.2 (2014): 261-271.

Wang, Chua-Chin, et al. "74-dBc SFDR 71-MHz four-stage pipeline ROM-less DDFS using factorized second-order parabolic equations." IEEE Transactions on Very Large Scale Integration (VLSI) Systems 27.10 (2019): 2464-2468.

Osmany .S. A., et. al. (2010), “An integrated 0.6–4.6 GHz, 5–7 GHz, 10–14 GHz, and 20–28 GHz frequency synthesizer for software-defined radio applications”, IEEE Journal of Solid-State Circuits, Vol. 45, No. 9, pp. 1657-1668.

Politis, Christos, et al. "SDR implementation of a testbed for real-time interference detection with signal cancellation." IEEE Access 6 (2018): 20807-20821.

Zhong, S., Feng, H., Zhang, P., Xu, J., Huang, L., Yuan, T., & Huo, Y. (2020). User oriented transmit antenna selection in massive multi-user MIMO SDR systems. Sensors, 20(17), 4867.

Thabit, A. A., & Ziboon, H. T. (2019, April). Design and implementation of a new detection system based on statistical features for different noisy channels. In Proceedings of the International Conference on Information and Communication Technology (pp. 81-88).

Rong .S., et. al. (2015), “A 0.05-to 10-GHz, 19-to 22-GHz, and 38-to 44-GHz Frequency Synthesizer for Software-Defined Radios in 0.13-$mumbox {m} $ CMOS Process”, IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 63, No. 1, pp. 109-113.

Marey, M., & Mostafa, H. (2021). Turbo modulation identification algorithm for OFDM software-defined radios. IEEE Communications Letters, 25(5), 1707-1711.

El Bahi, F. Z., HichamGhennioui, and MohcineZouak. "Real-time spectrum sensing of multiple OFDM signals using low cost sdr based prototype for cognitive radio." 2019 15th International Wireless Communications & Mobile Computing Conference (IWCMC). IEEE, 2019.

Ismaili .Z.E.A., et. al. (2017), “A 0.13 ?m CMOS fully integrated 0.1? 12 GHz frequency synthesizer for avionic SDR applications”, In 2017 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-4. IEEE.

Liu .D., et. al. (2018), “A quadrature single side-band mixer with passive negative resistance in software-defined frequency synthesizer”, Sensors, Vol. 18, No. 10, pp. 3455.

Zhou J., et. al. (2011), “A dual-mode VCO based low-power synthesizer with optimized automatic frequency calibration for software-defined radio”, In 2011 IEEE International Symposium of Circuits and Systems (ISCAS), pp. 1145-1148. IEEE.

Li Haominget. al. (2019), “A 210fs RMS jitter 187.5 MHz-3GHz fractional-N frequency synthesizer with quantization noise suppression techniques and chopping differential charge pump for SDR applications”, Microelectronics Journal, Vol. 85, pp. 135-143.

Dinesh, R., & Marimuthu, R. (2020). An analysis of ADPLL applications in various fields. Indonesian Journal of Electrical Engineering and Computer Science, 18(2), 856-866.

Koskin .E., et. al. (2020), “FPGA Validation of Event-Driven ADPLL”, In 2020 European Conference on Circuit Theory and Design (ECCTD), pp. 1-4. IEEE.

Bissa .P .R and Kirti .S .P (2018), “All Digital Phase Locked Loop for Low Frequency Applications”, In 2018 International Conference on Advances in Computing, Communications and Informatics (ICACCI), pp. 813-819. IEEE.

Chaharboor .M., et. al. (2018), “New approach of constructing ADPLL by a novel Quadrature Ring Oscillator using Low-Q Series LC tanks”, International Academic Journal of Science and Engineering, Vol. 5, No. 2, pp. 154-170.

Radhapuram .S., et. al. (2019), “Design and Emulation of All-Digital Phase-Locked Loop on FPGA”, Electronics, Vol. 8, No. 11, pp.1307.

Chen, X., Breiholz, J., Yahya, F. B., Lukas, C. J., Kim, H. S., Calhoun, B. H., & Wentzloff, D. D. (2019). Analysis and design of an ultra-low-power bluetooth low-energy transmitter with ring oscillator-based ADPLL and 4$times $ frequency edge combiner. IEEE Journal of Solid-State Circuits, 54(5), 1339-1350.

Du, Jianglin, et al. "A reference-waveform oversampling technique in a fractional-N ADPLL." IEEE Journal of Solid-State Circuits 56.11 (2021): 3445-3457.

Deng, Xiaoying, Huazhang Li, and Mingcheng Zhu. "A Novel Fast-Locking ADPLL Based on Bisection Method." Electronics 10.12 (2021): 1382.