# A Single Phase Five Level Inverter based on switched DC sources with Reduced Number of Total Component Count by Novel Topology

Mrs. Bharati S.Mathapati Student, Department of Electrical Engineering A.I.S.S.M.S.I.O.I.T, Kennedy Road Pune,India soni.mathapati@gmail.com

Prof.Pushkaraj V.Sakhare Professor, Department of Electrical Engineering V.V.P.I.E.T, Bijapur Road Solapur,India pushkaraj003@rediffmail.com Prof. Shubhangi S.Landge Professor, Department of Electrical Engineering A.I.S.S.M.S.I.O.I.T, Kennedy Road Pune,India shubhangi.landge1@gmail.com

Mr.Jadhav Dnyaneshwar N. Project Manager Finearc Systems Pvt.Ltd, Pune,India jadhavdnyaneshwar24@gmail.com

Abstract—A Single Phase Multilevel Inverter is designed to reduce the number of power switch requirement and gate drive circuit. So, it reduces total component count in the circuit than other conventional converters for the same level. In this topology, two DC supply and six switches are used to get five level output. In case of Cascaded H-Bridge Inverter, two DC sources and eight Power switches are required for getting five level. A multilevel voltage-source inverters are the unique solution for high power dc-to-ac conversion applications. A multilevel inverter is a linkage structure of multiple input dc levels and power semiconductor devices to get a quasisquare or staircase waveform. In addition, the multilevel waveform has a less harmonic contents as compared to a two-level waveform obtained from conventional inverters. The quality of the multilevel waveform is improved by increasing the number of levels. But, If number of level increases, a large number of power semiconductor devices and gate driver circuits are also increased. So, it will increases system complexity , cost and it will reduces the system reliability and efficiency. So, it is necessary to reduce the number of switches and gate driver circuits by using new topology. This paper presents a single phase five level inverter that has reduced total component count. It consists two step down transformer and two bridge rectifier to provide DC voltage to inverter circuit. This Inverter topology is mainly divided in three parts namely control circuit, gate drive circuit and power circuit. These all the circuits are explained in this paper. The topology is investigated through simulations and validated experimentally on a laboratory prototype.

Keywords: A single phase five level inverter, reduced total component count, reduced power switching devices, total harmonic

\*\*\*\*

# I. INTRODUCTION

Multilevel inverter technology is a very important alternative in high-power medium voltage applications. Researchers are going on to enhance their capabilities further through optimized control techniques, and to minimize both component count and manufacturing cost. The multilevel inverters have implemented in various applications, such as motor drives, power conditioning devices, renewable energy distribution. PWM inverters generation and can simultaneously control frequency, output voltage and it can reduce the amount of harmonics in output current which results in better THD content.

Several multilevel topologies have been developed, but increase in number of levels, it also increases the number of independent dc sources , number of switches, , switching stresses and switching losses.

A multilevel inverter consists multiple input DC sources

and capacitors and power semiconductor devices to produce a quasi square waveform. The Quality of output voltage waveform of a MLI shows how much close in shape the waveform to the required sine wave. The Quality of output voltage waveform of a MLI can be enhanced or improved by increasing the number of levels. So, it results in a large number of power semiconductor devices and gate driver circuits. Therefore, system complexity and cost will be increased and system reliability and efficiency will be reduced. So, for multilevel inverters having higher number of levels in output voltage waveform, practical considerations necessitate reduction in the number of gate driver circuits and switches.

This paper is organized as follows. Section II presents structure and operating modes of A Single Phase Five Level Inverter with Reduced Number of Total Component Count. Section III presents simulation and results of a single phase five level inverter with reduced number of total component count. Section IV presents hardware implementation and results of a single phase five level inverter with reduced number of total component count. In Section V conclusions are summarized.

#### **II. STRUCTURE AND OPERATING MODES OF** SINGLE PHASE FIVE LEVEL INVERTER WITH **REDUCED NUMBER OF TOTAL COMPONENT** COUNT

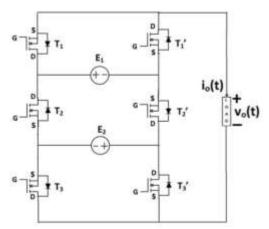

Figure 2.1: Single phase five level inverter with reduced number of total component count

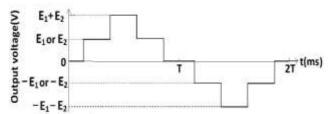

Figure 2.2: Output voltage waveform of Single phase five level inverter with reduced number of total component count

|   |                            | Т3                                                    | T1'                                                   | Т2'                                                   | Т3'                                                   | Output<br>Voltage                                     |

|---|----------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| 0 | 0                          | 0                                                     | 1                                                     | 1                                                     | 1                                                     | 0                                                     |

| 1 | 1                          | 1                                                     | 0                                                     | 0                                                     | 0                                                     | 0                                                     |

| 1 | 0                          | 0                                                     | 0                                                     | 1                                                     | 1                                                     | E1                                                    |

| 0 | 0                          | 1                                                     | 1                                                     | 1                                                     | 0                                                     | E2                                                    |

| 1 | 0                          | 1                                                     | 0                                                     | 1                                                     | 0                                                     | E1+E2                                                 |

| 0 | 1                          | 1                                                     | 1                                                     | 0                                                     | 0                                                     | -E1                                                   |

| 1 | 1                          | 0                                                     | 0                                                     | 0                                                     | 1                                                     | -E2                                                   |

| 0 | 1                          | 0                                                     | 1                                                     | 0                                                     | 1                                                     | -E1-E2                                                |

|   | 1<br>1<br>0<br>1<br>0<br>1 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

2.1: Modes of Operations

A Single phase five level inverter with reduced number of total component count is shown in Fig. 2.1. It consists two isolated input DC sources namely  $E_1$  and  $E_2$  ( $E_1=E_2$ ). There are 3 complementary pairs of power switching devices(N-Channel MOSFETs) which are denoted by  $(T_1, T_1')$ ,  $(T_2, T_2')$  and  $(T_3, T_2)$  $T_3$ ). The output voltage across load and load current are denoted by Vo (t) and Io (t) respectively. The reference polarities of the output voltage V<sub>o</sub>(t) and reference direction of load current  $I_0(t)$  are shown. The output voltage waveform of a single phase five level switched DC sources inverter when E1=E2 is shown in Fig. 2.2. The output voltage waveform consists of five levels 0,  $E_1$  or  $E_2$ ,  $E_1 + E_2$ ,  $-E_1$  or  $-E_2$ ,  $-E_1-E_2$ . The Time period of output voltage is 2T.

There are eight modes of operations for single phase five level switched DC source .The Modes of operation are explained below:

Mode 1:

In mode 1, The switches T1', T2' and T3' are turned on. So, no source is connected to the load. So, Output voltage across load is zero.

#### Mode 2:

In mode 2, The switches T1, T2 and T3 are turned on. So, no source is connected to the load. So, Output voltage across load is zero.

Mode 3:

In mode 3, The switches T1, T2' and T3' are turned on. So, Output voltage across load is +E1.

Mode 4:

In mode 4, The switches T1', T2' and T3 are turned on. So, Output voltage across load is +E2.

Mode 5:

In mode 5, switches T1, T2' and T3 are turned on. So, Output voltage across load is E1 + E2.

Mode 6:

In mode 6, switches T1', T2 and T3 are turned on. So, Output voltage across load is -E1.

Mode 7:

In mode 7, The switches T1, T2 and T3' are turned on. So, Output voltage across load is -E2.

Mode 8:

In mode 8, switches T1', T2 and T3' are turned on. So, Output voltage across load is -E1-E2.

# **III. SIMULATION AND RESULTS**

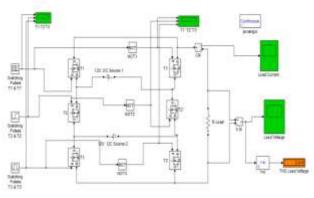

Figure 3.1: MATLAB simulation diagram of A Single Phase Five Level Inverter with Reduced Number of total **Component Count**

The MATLAB simulation diagram for A Single Phase Five Level Inverter with Reduced Number of Total Component Count is shown in fig. 3.1. This inverter is designed for 5 level. So, By applying following formula, The number of DC source requirement is calculated.

N=2n+1 5=2n+1

So, n=2 [Here, N: Number Of Level, n= Number Of DC source requirement]

In this type of Inverter, total 6 switches are required. It is found by Following Formula, Power switch requirement=2n+2

Here two DC sources are used to form single phase five level Switched DC source Inverter. So, Power switch requirement is 6. These six switches are connected through the two DC sources. The positive terminal of preceding source is connected to negative terminal of succeeding source and vice versa. The voltage of individual DC source is 12V. The three PWM pulses are given to the T1,T2 & T3. .These signals are inverted by using Not and given to T1',T2' & T3'. The one scope are provided to see pulses across T1,T2 & T3 and The another scope is provided to see pulses across T1',T2' & T3'. The resistive load is connected in circuit. Current measurement block is connected in series with load for measuring load current. The volt measurement block is connected across load for measuring output load voltage. The THD block in figure is connected to measure total harmonic distortion in output voltage. The scopes are connected to display Output voltage and output current.

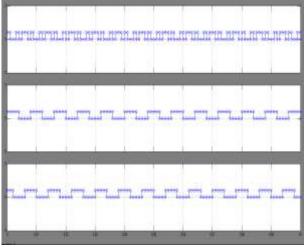

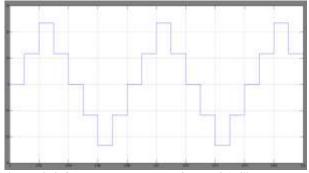

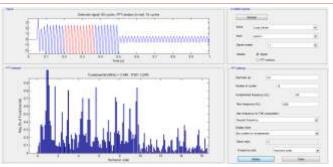

The switching sequence for MATLAB simulation is given in Table 3.1. The gate pulses provided to all switches for triggering is shown in fig. 3.2. and fig. 3.3. The Output voltage waveform of single phase five level Cascaded H-Bridge inverter is shown in Fig.3.4. Fig.3.5 shows the Output Current waveform of single phase five level Cascaded H-Bridge inverter. The output voltage is 24V, output current is 2.4A and Total Harmonic distortion is 3.59%.

| Mode | <b>T</b> <sub>1</sub> | <b>T</b> <sub>2</sub> | <b>T</b> <sub>3</sub> | <b>T</b> <sub>1</sub> ' | $\mathbf{T_2}$ | T3 | V0     |

|------|-----------------------|-----------------------|-----------------------|-------------------------|----------------|----|--------|

|      |                       |                       |                       |                         |                | ,  |        |

| 1    | 0                     | 0                     | 0                     | 1                       | 1              | 1  | 0      |

| 3    | 1                     | 0                     | 0                     | 0                       | 1              | 1  | E1     |

| 5    | 1                     | 0                     | 1                     | 0                       | 1              | 0  | E1+E2  |

| 4    | 0                     | 0                     | 1                     | 1                       | 1              | 0  | E2     |

| 2    | 1                     | 1                     | 1                     | 0                       | 0              | 0  | 0      |

| 6    | 0                     | 1                     | 1                     | 1                       | 0              | 0  | -E1    |

| 8    | 0                     | 1                     | 0                     | 1                       | 0              | 1  | -E1-E2 |

| 7    | 1                     | 1                     | 0                     | 0                       | 0              | 1  | -E2    |

Table 3.1: Switching sequence for MATLAB simulation

Figure 3.2: Gate pulses to T1,T2,T3

Figure 3.3: Gate pulses to T1',T2',T3'

Figure 3.4:Output voltage waveform of A Single Phase Five Level Inverter with Reduced Number of total Component Count

Figure 3.5:Output Current waveform of A Single Phase Five Level Inverter with Reduced Number of total Component Count

Fig.3.6: FFT analysis of single phase five level Switched DC Source inverter

IV. HARDWARE IMPLEMENTATION AND RESULTS

Figure 4.1: Hardware Set Up for single phase five level Inverter With reduced Number of total component count

A Single Phase Five Level Inverter with Reduced Number of total Component Count is mainly divided in three parts:

- 1) Control Circuit

- 2) Gate drive Circuit

- 3) Power Circuit

- **1)** CONTROL CIRCUIT:

**Figure 4.2: Control Circuit**

A PIC 16F877a controller is used in Control circuit of Single phase five level Inverter to provide the logic signals

IJRITCC | June 2017, Available @ http://www.ijritcc.org

to Switch on and Switch off the power MOSFETs. A PIC 16F877a requires a five volt DC supply. So, here 230V Supply from mains is stepped down to 12V by using step down transformer. A 12V AC supply is converted into 12V DC by Bridge rectifier. By using voltage regulator [7805],12V DC supply is converted into 5V DC supply. This 5V DC is filtered by filtering capacitor. The 5V DC supply obtained by Voltage regulator is given to PIC controller Through the pin number 8. From PIC 16F877a controller, six pulses are given to Gate drive circuit i.e. to TLP250 IC .These pulses are provided from Port C(RC2-RC7) from Controller. The Pin numbers through which pulses are provided are 17,18,23,24,25 and 26. The crystal oscillator is used to provide the switching frequency upto 4MHZ.LED are used for indication purposes. A PIC 16F877a controller consists a timer to turn on and turn off the devices. This controller provides a Current in miliampere, six outputs can be drawn to give pulses to gate drive circuits, it also consists Timer, so This controller is used to design A Single phase Five level Inverter.

# **2)** GATE DRIVE CIRCUIT:

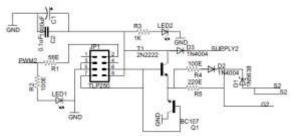

**Figure 4.3: Gate Drive Circuit**

It consist six number of TPL250 IC to drive six IRF840 MOSFET. So, it is called Gate drive IC.Each gate drive circuit is used to switch only one power switch. A multi tapping step down transformer is used to provide 12V supply to all six TLP 250 IC.A TLP250 IC get two signals, First is 5V,15mA logic signal is from PIC 16F877a Controller to the pin number 2 of TLP 250. The Second is from step down transformer to the pin number 8 of TLP 250. The 12V AC from step down transformer is half rectified by one diode, then it filtered by capacitor, another diode is used for full rectification. This 12 V DC is given to gate of N-channel MOSFET. But its current is too much low. The gate of MOSFET requires 12V,100mA supply. So, Darlington pair transistor is used to amplify the current up to 100mA.

The transistor has three terminals namely Emitter, Collector and Base. The emitters of both transistor are connected common and they are grounded. The 12V DC supply is given to Collector terminal. The resistors are used for current limiting. The TLP 250 magnify the voltage from 5V to 12V and Darlington pair transistor amplify the current from 15mA to 100mA.Finally, 12V,100mA supply is given to the gate of MOSFET for switching.The Zener diode is provided for protection purpose. If due to any reason, above 12V voltage goes to gate of MOSFET, then it will get damage. So, Zener diode is provided. A simple diode is also used in Output of gate drive circuit to maintain switching frequency.When MOSFET will On, then capacitor in the MOSFET get charged, When MOSFET will off, then it discharges through that simple diode. Then next mode will be operated.

## **3)POWER CIRCUIT:**

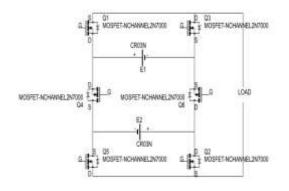

Figure 4.4: Power circuit

These six MOSFET are connected through the DC sources in such a way that the positive terminal of preceding source is connected to negative terminal of succeeding source and that the Negative terminal of preceding source is connected to Positive terminal of succeeding source. This inverter is designed for five level, so six MOSFET and two DC sources are used. This inverter designed for the output voltage 24V. The resistive load is connected in circuit whose value is  $4K\Omega$ . In this topology, two step down transformers are used to step down the voltage from 230V to 12V. This 12V AC supply is converted into 12V DC. Then two filtering Capacitors are used for getting pure DC to Inverter. The switching signals for Turn On and Turn off process of MOSFET are provided by Control circuit and according to that signals, MOSFET are driven by Gate drive circuit.

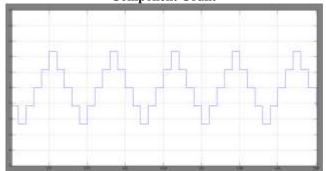

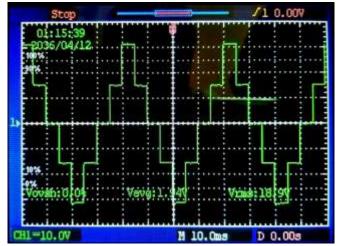

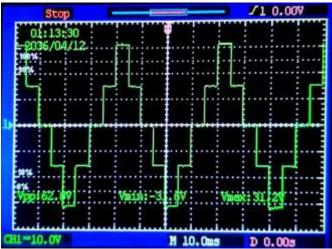

Figure 4.5. Output Voltage Waveforms on DSO with Vavg and Vrms

Figure 4.6: Output Voltage Waveforms on DSO with Vpp , Vmin and Vmax

The Hardware Testing Results of A Single Phase Five Level Inverter with Reduced Number of total Component Count are shown in above figures. From this testing results, it is clear that this type of inverter gives five level and it will operates in eight modes. Fig. 4.1 shows Laboratory Set up for A Single Phase Five Level Inverter with Reduced Number of total Component Count while testing. Fig. 4.4 shows Schematic diagram of power circuit of single phase five level Inverter. Fig. 4.5 reveals Output Voltage Waveforms on DSO with Vavg and Vrms . Fig. 4.6 shows Output Voltage Waveforms on DSO with Vpp ,Vmin and Vmax.

## **V. CONCLUSION**

A Single Phase Five Level Inverter with Reduced Number of Total Component Count by Novel Topology is investigated through the simulations and validated experimentally on a laboratory prototype. The number of Power switch requirement and Gate drive Circuits are also reduced in this Inverter than the other conventional inverter. So, The total Component count is reduced in this topology. It reduces total cost and complexity of the system. It also increases the system reliability and efficiency.

#### **VI. REFERENCES**

- J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 655–667, Feb. 2012.

- [2] Krishna Kumar Gupta, and Shailendra Jain, "A novel multilevel inverter based on switched DC sources,"IEEE Trans. on Ind. Electron., vol. 61,no.7, pp. 3269-3278, July 2014.

- [3] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 57,no. 7, pp. 2197–2206, Jul. 2010.

- [4] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 655–667, Feb. 2012.

- [5] G. Buticchi, E. Lorenzani, and G. Franceschini, "A five-level single-phase grid-connected converter for renewable distributed systems," IEEE Trans.Ind. Electron., vol. 60, no. 3, pp. 906–918, Mar. 2013.

- [6] K.A.Corzine, M.W. Wielebski, F.Z Peng, and J.Wang, "Control of cascaded multilevel inverters", IEEE Trans. Power Electron vol.19,no.3 ,pp.732-738,,May 2004.

- [7] Ebrahim Babaei "A Cascaded Multilevel converter Topology With Reduced Number of Switches", IEEE Trans. Power Electron vol.23,no.6,Nov 2008

- [8] Manjrekar MD, Lipo TA. "A hybrid multilevel inverter topology for drive applications", Proceeding IEEE International Conference, 1998,2:523–9.

- [9] G. Buticchi, E. Lorenzani, and G. Franceschini, "A five-level single-phasegrid-connected converter for renewable distributed systems," IEEE Trans.Ind. Electron., vol. 60, no. 3, pp. 906– 918, Mar. 2013.

- [10] Y. Hinago and H. Koizumi, "A switched-capacitor inverter using series/ parallel conversion with inductive load," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 878–887, Feb. 2012.

- [11] 1999 E. Najafi and A. H. M. Yatim, "Design and implementation of a new multilevel inverter topology," IEEE Trans. Ind. Electron., vol. 59, no. 11, pp. 4148–4154, Nov. 2012.