# Review of Clocked Storage Elements in Digital Circuit Design

Ayushi Nagar

M.Tech scholar

Department of Electronics and Communication

SISTec, Bhopal (M.P.)

Prof. Rahul Shrivastava

Assistant Professor

Department of Electronics and Communication

SISTec, Bhopal (M.P.)

ISSN: 2321-8169

30 - 34

Abstract—Storage of digital circuit is "state" or memory. These are called sequential circuits. The most fundamental sequential circuit type that we will ponder is known as the Flip-Flop. It is ponder four distinct assortments of these gadgets and their utilization in registers and register documents, which can be considered as one type of on—CPU memory. The traditional memory, called RAM, is ordinarily not on the CPU chip. Regular Slam and its assortments, including RAM, ROM, SRAM, Measure, and SDRAM. True single-phase clock (TSPC) method of reasoning has found wide use in advanced plan. At first as a quick topology, the TSPC structure in like manner eats up less power and includes less areas than various systems. In flip-flop plan only a single transistor is being clocked by short heartbeat get ready which is known as True Single Phase Clocking (TSPC) flip-flop.

Keywords- RAM, ROM, SRAM, DRAM, TSPC, VLSI, Flip-Flop, Clock

\*\*\*\*

### I. INTRODUCTION

True Single Phase Clock (TSPC) is a general unique flip-flop that works at fast and expends low power. The capacity of a clocked storage component is to catch the data at a specific minute in time and protect it as long as it is required by the advanced framework. Having said as much, it is unimaginable to expect to characterize a storage component without characterizing its relationship to a clocking instrument in a computerized framework, which is utilized to decide discrete time occasions. This definition is general and ought to incorporate different methods for executing an advanced framework. All the more especially the component that decides time in a synchronous framework is the clock.

A clock signal is delivered by a clock generator. Albeit increasingly complex game plans are utilized, the most widely recognized clock signal is as a square wave with a half obligation cycle, generally with a fixed, consistent recurrence. Circuits utilizing the clock signal for synchronization may end up dynamic at either the rising edge, falling edge, or, on account of twofold information rate, both in the rising and in the falling edges of the clock cycle.

Numerous cutting edge microcomputers utilize a "clock multiplier" which increases a lower recurrence outside clock to the fitting clock rate of the microchip. This enables the CPU to work at an a lot higher recurrence than the remainder of the PC, which manages execution gains in circumstances where the CPU does not have to look out for an outside factor (like memory or information/yield).

The clock dissemination system (or clock tree, when this system frames a tree) circulates the clock signal(s) from a typical point to every one of the components that need it. Since this capacity is essential to the activity of a synchronous framework, much consideration has been given to the qualities of these clock signals and the electrical systems utilized in their conveyance. Clock signals are regularly viewed as

straightforward control signals; in any case, these signals have some extraordinary qualities and properties.

Clock signals are normally stacked with the best fanout and work at the most noteworthy velocities of any signal inside the synchronous framework. Since the information signals are given a transient reference by the clock signals, the clock waveforms must be especially perfect and sharp. Moreover, these clock signals are especially influenced by innovation scaling (see Moore's law), in that long worldwide interconnect lines become essentially progressively resistive as line measurements are diminished. This expanded line opposition is one of the essential purposes behind the expanding importance of clock appropriation on synchronous execution. At long last, the control of any distinctions and vulnerability in the entry times of the clock signals can seriously restrain the greatest execution of the whole framework and make cataclysmic race conditions in which an inaccurate information signal may hook inside a register.

Most synchronous advanced frameworks comprise of fell banks of sequential registers with combinational rationale between each arrangement of registers. The practical necessities of the computerized framework are fulfilled by the rationale stages. Every rationale arrange presents defer that influences timing execution, and the planning execution of the computerized structure can be assessed with respect to the planning necessities by a planning examination. Regularly extraordinary thought must be made to meet the planning prerequisites. For instance, the worldwide execution and nearby planning prerequisites might be fulfilled by the watchful addition of pipeline registers into similarly divided time windows to fulfill basic most pessimistic scenario timing limitations. The best possible plan of the clock dispersion arrange guarantees that basic planning necessities are fulfilled and that no race conditions exist.

Notwithstanding combinatorial rationale some kind of storage is required for an advanced circuit to keep its inner state. Static information storage is practiced with bi-stable circuits.

essential computerized static storage components, the hook and the register or purported D-flip-flop (the inverters to create the supplement of the clk signals are not appeared). The latch is straightforward for the information D amid the clock-high period, while the register really tests the information at the rising edge of the clk signal. Another case of a static storage component is the RS (reset-set) flip-flop. The two locks and registers are utilized to actualize synchronous computerized. digital.

### II. LITERATURE SURVEY

Y. Cai et al., [1] Flip-flops (FFs) are fundamental structure squares of sequential computerized circuits however commonly possess a considerable extent of chip territory and devour noteworthy measures of intensity. This paper proposes 18-transistor single-phase clocked (18TSPC), another topology of completely static conflict free single-phase clocked (SPC) FF with just 18 transistors, the most reduced number announced for this sort. Actualized in 65-nm CMOS, it accomplishes 20% cell region decrease contrasted with the customary transmission entryway FF (TGFF). Reenactment results demonstrate the proposed 18TSPC is multiple times more proficient than TGFF in the vitality defer space. To show EDA similarity and circuit/framework level advantages, a move register and an AES-128 encryption motor have been executed. Chip trial estimations at 0.6 V, 25 °C demonstrate that, contrasted with TGFF, the proposed 18TSPC accomplishes decreases of 68% and 73% in by and large and clock dynamic power, individually, and 27% lower spillage.

W. Wang et al., [2] Two low voltage double modulus recurrence divider dependent on expanded true single-phase clock (E-TSPC) rationale are proposed. By lessening the quantity of sequential transistors from VDD to GND, the proposed structures can viably work at low voltage. Reenactment results in SMIC 40nm innovation demonstrate that the exhibited structure I has better power and speed execution with lower supply voltage. Contrasted with the referenced structures, the introduced plan II can work at the most minimal supply voltage with little loss of execution.

J. Shaikh et al., [3] Positron outflow tomography (PET) is an atomic utilitarian imaging strategy that delivers a threedimensional picture of useful organs in the body. PET requires high goals, quick and low power multichannel simple to advanced converter (ADC). A regular multichannel ADC for PET scanner design comprises of a few squares. The vast majority of the squares can be planned by utilizing quick, low power D flip-flops. A preset-capable true single phase clocked (TSPC) D flip-flop demonstrates various glitches (commotion) at the yield because of pointless flipping at the middle of the road hubs. Preset-capable changed TSPC (MTSPC) D flip-flop have been proposed as an elective answer for ease this issue. Be that as it may, the MTSPC D flip-flop requires one additional PMOS to suspend flipping of the halfway hubs. In this work, we planned a 7-bit preset-capable dark code counter by utilizing the proposed D flip-flop. This work includes UMC 180 nm CMOS innovation for preset-capable 7-bit dim code counter where we accomplished 1 GHz greatest task recurrence

with most noteworthy piece (MSB) postpone 0.96 ns, control utilization 244.2  $\mu W$  (smaller scale watt) and power defer item (PDP) 0.23 pJ (Pico joule) from 1.8 V control supply.

P. Xu et al., [4] True Single Phase Clocked (TSPC) flip-flops (FF) are generally utilized in high-recurrence dividers for their higher task speed and lower control contrasted with Ace Slave owner FFs. In this paper, we examine the enhancement of TSPC recurrence dividers for dependably on low-recurrence clock division in ultra-low-control (ULP) SoCs. We dissect the design, task rule and information misfortune issue in TSPC-based recurrence divider. An improvement procedure dependent on specific door length upsize is proposed to limit control utilization by adjusting exchanging and spillage control utilization. A 10-arrange recurrence divider was structured in 28 nm FDSOI CMOS and coordinated in a ULP SoC. Post-design reproductions with 32-MHz input recurrence demonstrate a power utilization of 28.3 nW with 0.8-V supply voltage.

F. Stas et al., [5] In this paper, we propose a 18-transistor (18T) True-Single-Phase-Clock (TSPC) Flip-Flop (FF) with static information maintenance dependent on two forward-contingent input circles, without expanding the clock load, in contrast with the benchmark TSPC design. The proposed FF was executed for ultra-low-voltage (ULV) activity in 28nm FDSOI CMOS. The exhibitions of the proposed FF separated from estimations of clock dividers are contrasted with reference plans including the customary M-S FF, the gauge TSPC FF and an as of late proposed retentive TSPC FF. Contrasted with the regular MS FF, the proposed FF demonstrates individually 5%, 60% and 30% upgrades at 0.4V in greatest recurrence, vitality/cycle and leakage power.

### III. TYPES OF STORAGE SYSTEM

### A. Latch based clocked storage elements

A most straightforward storage component comprises of an inverter pursued by another inverter giving a positive criticism as appeared in Figure. 1 (a). The data bit at the info is in this way bolted because of the positive criticism circle and it very well may be just changed "by power", (for example by constraining the yield of the input inverter to take another rationale esteem). This arrangement is in all respects much of the time utilized and is otherwise called the "keeper", — a circuit that keeps (protects) the data on a specific hub.

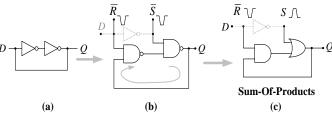

If we somehow managed to stay away from the power dissemination related with overwhelming (compelling), the attendant to change its esteem, we should present hubs that will help us in changing the rationale esteem put away in the criticism circle. For that reason we are allowed to utilize rationale NAND or NOR entryways, as appeared in Fig.1. Especially fascinating is a straightforward adjustment of the chart, which features the Aggregate of-Items nature of this rationale topology. We begin with a straightforward cross-coupled inverter pair which is unrolled to all the more likely delineate the positive input that exists. In the second step we supplant the inverters with NAND doors which empowers us

to control the variable inside the circle and to specifically set it to "1" or "0" utilizing the information which controls the entryway S and R for this situation (as appeared in Fig. 1.b). At long last we apply De Morgan rules which enables us to change this structure into As well as topology. It is outstanding in advanced plan that this topology speaks to Aggregate of-Items (SOP), hence a general articulation for any Boolean capacity.

Figure 1: Latch structure: (a) keeper (b) S-R latch (c) SOP latch

A latch can be worked in an Entirety of-Item topology (Fig. 1 (c). This discloses to us that it is conceivable to fuse rationale into the lock, given that the Total of-Items is one of the essential acknowledge of the rationale work.

It is anything but difficult to determine a Boolean condition speaking to a conduct of the exhibited S-R hook. The following yield Qn+1 is a component of Qn, S and R signals. Later in this book we will misuse those straightforward conditions so as to configuration improved clocked storage components. Displayed S-R hook can change the yield Q anytime.

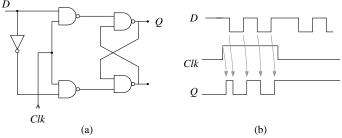

Figure 2: (a) Clocked D-Latch (b) timing diagram of clocked D-Latch So as to make it perfect with the synchronous structure we will confine when Q can be influenced by presenting the clock signal which entryways S and R inputs. On the off chance that the information input D is associated with S, and the property of S-R lock, which makes S and R totally unrelated is connected, the subsequent D hook is appeared in Fig. 2 (a). The related planning graph of a D-Hook is appeared in Fig. 2 (b). The hook is straightforward amid the timeframe in which clock is dynamic, – for example expecting rationale 1 esteem.

## B. True-Single-Phase-Clock (TSPC) latch

This latch was developed by combining two sections comprising of CMOS Domino and CMOS NORA rationale. Amid the dynamic clock (Clk=1), CMOS Domino assesses the contribution to a monotonic style (just a progress from rationale 0 to 1 is conceivable), while NORA rationale is precharging. On the other hand, amid dormant clock (Clk=0)

Domino is being pre-charged (hence is non-straightforward) while NORA is assessing its information. The mix of NORA and Domino rationale stages results in a non-straightforward Ace Slave latch that requires just a single clock. Thus the name given to it was True-Single Phase Clock hook (TSPC).

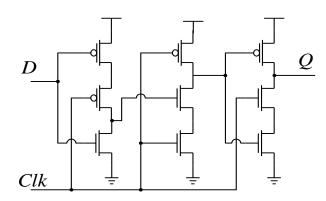

Figure. 3: True Single Phase Clock (TSPC) Latch introduced by Yuan and Svensson

The task of TSPC latch is represented in Fig. 3. Whenever principal reversal organize L1, is the straightforward and the second half L2 of TSPC is precharged. In this manner, toward the finish of the half-cycle amid which Clk=0, the info D is available at the contribution of the Domino hinder as its supplement . At the point when the clock changes to rationale 1 (Clk=1), Domino rationale assesses and the yield either remains at rationale 0 or makes progress from 0 to 1 contingent upon the tested information esteem . This change can't be turned around until the following clock cycle. In actuality the primary inverter associated with the information goes about as an Ace Hook, while the second (Domino) arrange goes about as a Slave Lock. The exchange from the Ace Hook to the Slave latch happens while the clock changes its incentive from rationale 0 to rationale 1. Along these lines, TSPC carries on as a "main edge" activated Flip-Flop. It is additionally often called a Flip-Flop, however by the idea of TSPC activity this grouping is wrong.

Figure 4: TSPC Latch operation

Because of its effortlessness and speed TSPC was an exceptionally mainstream method for actualizing clocked storage component. Be that as it may, TSPC displayed affectability to glitches made by the clock edges. This glitch is shown on the yield holding a rationale estimation of "1", while the info is accepting D=0.

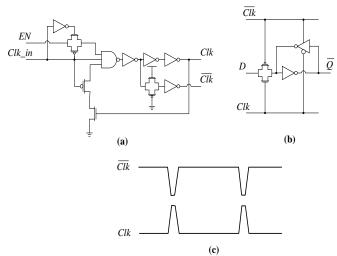

### C. Pulse Register Single Latch

Recognizing the overhead forced by Ace Slave hook structure and the potential "signal race" risks presented by a single-lock plan, a thought of a single latch configuration clocked by privately produced short heartbeats developed. The thought is to make a clock beat short and in this manner diminish the time window amid which the latch is straightforward. In any case, there exist a danger of a "short way" that might be caught amid a similar clock. Given that the clock beat is short, this peril is diminished and it is additionally conceivable to "cushion" the rationale (include inverters) in those ways with the goal that they would not speak to an issue. Such a short clock beat can't be circulated universally on the grounds that the clock dispersion system would assimilate it. There is an extra threat on the grounds that because of the procedure varieties, the length of that clock heartbeat will fluctuate locally on the chip, and from chip to chip. So as to moderate these issues, the beat clock is created locally and it as a rule drives a register comprising of a few such single-locks found physically extremely near one another. This technique would free its points of interest of effortlessness and low power if each and every latch would require separate clock generator as observed from Fig. 5 (an) and (b).

Figure 5: Pulse Latch: (a) local clock generator, (b) single latch (c) clock signals

The clock created by nearby clock generator must be sufficiently wide to empower the latch to catch its information. In the meantime it must be adequately short to limit the likelihood of "basic race". Those clashing necessities utilize such single-hook plan unsafe by diminishing the power and unwavering quality of such structure. By and by, such structure has been utilized because of the basic need to diminish cycle overhead forced by the clocked storage components. Intel's rendition of Beat Hook is appeared in Fig.6. Another advantage of this plan is low power utilization because of the

normal clock signal generator and a straightforward structure of the latch.

### D. Flip-Flop

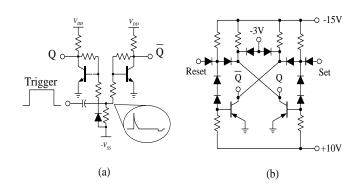

The principle highlight of the Flip-Flop is that the way toward catching information is identified with the progress of the clock (from 0- to-1 or from 1-to-0), in this manner the Flip-Flop isn't straightforward. In this manner Flip-Flop based frameworks are simpler to show and the planning devices discover Flip-Flop based frameworks more straightforward and less hazardous to break down. The exact point in time when information is caught is dictated by the clock occasion assigned as either driving or trailing edge of the clock. In different words, the change of the clock from rationale 0-to-1 makes information be caught (it is the 1-to-0 progress in the trailing edge activated Flip-Flop). When all is said in done, Flip-Flop isn't straightforward since it is expected that the clock progress is practically prompt. As we will see later, even the Flip-Flop can have a little time of straightforwardness related with the restricted time window amid which the clock changes, as it will be examined later. When all is said in done we treat Flip-Flop as a non-straightforward clocked storage component. Given that the activating component of a Flip-Flop is the progress of the clock signal, there are a few different ways of inferring the Flip-Flop structure. For better comprehension of its usefulness it takes a gander at an early form of the Flip-Flop, appeared in Fig.6, and utilized in early PCs and computerized frameworks. The beat, which causes the change, is gotten from the activating signal (additionally alluded to as "trigger") by utilizing a straightforward differentiator comprising of a capacitor C and resistor R. One can likewise comprehend a risk presented by the Flip-Flop. On the off chance that the activating signal change is moderate, a heartbeat inferred along these lines may not be fit for setting off the Flip-Flop. Then again, even a little glitch on the trigger line may cause a false triggering.

Figure.6: (a) Early version of a Flip-Flop (b) PDP-8 direct Set-Reset sequential element

To expound in further comprehension of the Flip-Flop it is useful to begin drawing the qualification between the Flip-Flop and the Lock based CSE. The Flip-Flop and the Hook work on various standards. While the Lock is "level-touchy" which means it is responding on the dimension (intelligent esteem) of the clock signal, Flip-Flop is "edge delicate", implying that the system of catching the information esteem on its info is identified with the progressions of the clock signal. Level affectability suggests that the lock is catching the information

amid the whole timeframe when the clock is dynamic (rationale one), along these lines the hook is straightforward. The two are intended to an alternate arrangement of prerequisites and in this way comprise of characteristically extraordinary circuit topologies.

### IV. CONCLUSION

Clocking is one of the most critical parts of each processor, often determining its performance and largely impacting its power consumption. The clocking subsystem and clocked storage elements in particular are responsible for an increasingly substantial portion of the circuit design improvements needed to accommodate the continuing scaling trends with each processor generation. In this paper an overview of clocking and design of clocked storage elements is presented. It shows how different clocked storage elements work against each other. TSPC is one of the storage systems which is using most of digital circuit system.

### **REFERENCE**

- [1]. Y. Cai, A. Savanth, P. Prabhat, J. Myers, A. S. Weddell and T. J. Kazmierski, "Ultra-Low Power 18-Transistor Fully Static Contention-Free Single-Phase Clocked Flip-Flop in 65-nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 54, no. 2, pp. 550-559, Feb. 2019.

- [2]. W. Wang, S. Jia, Z. Wang, T. Pan and Y. Wang, "Low Voltage Dual-Modulus Frequency Divider Based on Extended True Single-Phase Clock Logic," 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, 2018, pp. 1-2.

- [3]. J. Shaikh and H. Rahaman, "High speed and low power presetable modified TSPC D flip-flop design and performance comparison with TSPC D flip-flop," 2018 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, 2018, pp. 1-4.

- [4]. P. Xu, C. Gimeno and D. Bol, "Optimizing TSPC frequency dividers for always-on low-frequency applications in 28nm FDSOI CMOS," 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, 2017, pp. 1-2.

- [5]. F. Stas and D. Bol, "A 0.4V 0.08fJ/cycle retentive True-Single-Phase-Clock 18T Flip-Flop in 28nm FDSOI CMOS," 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, 2017, pp. 1-4.

- [6]. J. Lin, M. Sheu, Y. Hwang, C. Wong and M. Tsai, "Low-Power 19-Transistor True Single-Phase Clocking Flip-Flop Design Based on Logic Structure Reduction Schemes," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 25, no. 11, pp. 3033-3044, Nov. 2017.

- [7]. H. Ashwini, S. Rohith and K. A. Sunitha, "Implementation of high speed and low power 5T-TSPC D flip-flop and its application," 2016 International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, 2016, pp. 0275-0279.

- [8]. S. Jia, Z. Wang, Z. Li and Y. Wang, "A novel low-power and high-speed dual-modulus prescaler based on extended true single-phase clock logic," 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, 2016, pp. 2751-2754.

- [9]. S. S. Varma, A. Sharma and B. Anand, "An efficient methodology to characterize the TSPC flip flop setup time for static timing analysis," 2016 13th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Lisbon, 2016, pp. 1-4.

- [10].S. Jia, S. Yan, Y. Wang and G. Zhang, "Design of low-power high-speed divide-by-2/3 prescalers with improved true single-phase clock scheme," 2014 Asia-Pacific Microwave Conference, Sendai, Japan, 2014, pp. 241-243.

- [11].X. Tang, J. Zhang, P. Gaillardon and G. De Micheli, "TSPC Flip-Flop circuit design with three-independent-gate silicon nanowire FETs," 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne VIC, 2014, pp. 1660-1663.

- [12].M. Jung, J. Fuhrmann, A. Ferizi, G. Fischer, R. Weigel and T. Ussmueller, "A 10 GHz low-power multi-modulus frequency divider using Extended True Single-Phase Clock (E-TSPC) Logic," 2012 7th European Microwave Integrated Circuit Conference, Amsterdam, 2012, pp. 508-511.

- [13].F. Stas and D. Bol, "A 0.4-V 0.66-fJ/Cycle Retentive True-Single-Phase-Clock 18T Flip-Flop in 28-nm Fully-Depleted SOI CMOS," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 3, pp. 935-945, March 2018.

- [14].J. Lin, M. Sheu, Y. Hwang, C. Wong and M. Tsai, "Low-Power 19-Transistor True Single-Phase Clocking Flip-Flop Design Based on Logic Structure Reduction Schemes," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 25, no. 11, pp. 3033-3044, Nov. 2017