# A Review of CMOS Fabrication Technology with Pipeline ADC

Priyanu Katiyar M.Tech Scholar,VLSI Dept. of ECE SISTec, Bhopal (M.P.) Prof. Vaibhav Jindal Assistant Professor Dept. of ECE SISTec, Bhopal (M.P.)

Dr. Paresh Rawat HOD Dept. of ECE SISTec, Bhopal (M.P.)

*Abstract*—Analog-to-digital converters (ADCs) are fundamental outline squares and are right now embraced in numerous application fields to show signs of improvement computerized frameworks, which achieve better exhibitions with deference than simple arrangements. With the quick headway of CMOS creation innovation, additionally flag handling capacities are executed in the computerized space for a lower cost, bring down power utilization, higher yield, and high re-configurability. In this paper show diverse simple to-computerized converter manufactured in a CMOS innovation. The Pipeline ADC engineering takes into account elite, low power ADCS to be bundled in little frame factors for the present applications. There is Wide range of ADC structures accessible relying upon the necessities of the application.

\*\*\*\*\*

Keywords- ADC, CMOS, VLSI, Pipeline

# I. INTRODUCTION

Sustained scaling into the nanometer administration faces a few obstacles. Assembling troubles yield gadgets with parameter varieties and since these gadgets are probably going to work near as far as possible, they are helpless to annoyances because of commotion. We allude to such CMOS gadgets whose conduct is probabilistic CMOS gadgets, or PCMOS gadget for short. Unmistakably, current circuit outline systems are deficient to plan strong circuits within the sight of these irritations, since they rely upon the gadgets with deterministic conduct. To outline hearty circuits and engineering within the sight of this (inescapable) factual conduct at the gadget level, it has been estimated that a move in the plan worldview—from the present day deterministic plans to measurable or probabilistic outlines without bounds would be important.

# II. LITERATURE SURVEY

Multi-stream gathering is a key point for future items in link modem, earthly and satellite television. This infers synchronous gathering of a few channels found any whereon the entire band or fractional RF band. This is a required component for watch-and-record, picture-in-picture, or fortified Channel applications.

The concurrent gathering assumes either the digitization of the entire band or the utilization of the same number of tuners as needed channels. The range of intrigue spreads from 50MHz to 1GHz, and one may need to all the while get up to 16 channels of 6MHz. Obviously, utilizing for example 16 tuners Coordinated Circuits for getting 16channels will be seriously over-executing regarding cost and power. Thusly it is of specific significance to research answers for the entire digitization of the 1GHz info range. Broadband digitization is to be sure a concentrated issue, for instance in [1]. Besides,

this is an anticipated heading in RF testing design: the entire RF band is examined from the get-go in the flag way. This lessens RF equipment, enables the vast majority of the preparing to be done in advanced area, accordingly Encourages reconfigure capacity by (Programming Radio).The surely understood Simple to-Computerized Converters (ADC) designs are not adjusted to such an application. Streak ADCs, pipeline ADCs, Progressive Guess Enroll (SAR) ADCs and  $\Sigma\delta$  ADCs are either rapid or high-goals. In the focused on application, we require both rapid and high-goals. As a goal, we think about the accompanying determinations, which are as per the Standardization [2] with an extra security edge.

The most extreme information recurrence being 1GHz, we select an examining recurrence of 2.2GHz. We likewise need a base Flag to-Commotion Proportion (SNR) of 50dB. This esteem prompts 10 bits of goals. Obviously, low utilization and exceedingly significant goals in such mass gadgets. ADCs are frequently portrayed by the examining rate and the goals. This last is characterized by the SNR and the Powerful Number of Bits (ENOB). Surface and power utilization are key components while tending to a market In the field of pipe line ADC various inquires about have been made on investigating more proficient pipe line ADC

J. Arias et .al proposed low power pipe line ADC for remote LAN and found that for transformation of any simple flag in 10 bit computerized utilizing this procedure control utilization is 10mWs when pipe line and time interleaving both engineering have been utilized for circuit manufactured with 0.25µm CMOS innovation with 12mW power supply It is a nine-organize 1.5-piece/arrange time-interleaved double pipeline converter [12]. One pipeline forms the even examples, while the other pipeline chips away at odd examples. The two pipelines share their operational intensifiers (operation amps) [9]. This establishes a vast power sparing, in light of the fact that operation amps are the most power-requesting squares, and limits balance and gain bungles between pipelines that could corrupt the ADC's execution

# A. MOSFET DEVICE OVERVIEW:

Here, we initially examine the fundamental structure, task and imperative terms identified with the center unit of CMOS i.e. MOSFET or basically MOS. The main effective MOS transistor would utilize metals for the door material, SiO2 (oxide) for separator and semiconductor for substrate. Therefore, this gadget was named MOS transistor. The name Field Impact Transistor (FET) alludes to the way that the entryway is turned on and off by the transistor with an electric field going through the door oxide.

# B. Structure of MOS:

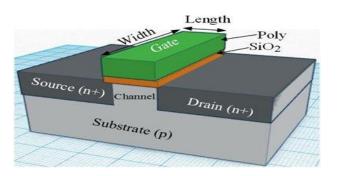

In light of the sort of directing channel, two sorts of MOS structures are obvious: n-channel and p-channel MOS. Here, we will just review the NMOS transistor on the grounds that the two transistors are reciprocal in nature.MOS transistor is a 4-terminal gadget having terminal channels, source, entryway and body (substrate). Figure 1 demonstrates the 3-dimentional structure of NMOS. The NMOS transistor is framed on a p-type silicon substrate (additionally called body). By embedding benefactor contaminations in opposite sides of the substrate, the source and the deplete are shaped. In Figure 1, these areas are meant by n+ which demonstrate overwhelming doping of benefactor polluting influences. This overwhelming doping results in low resistivity for these areas.

### Figure 1. Structure of NMOS transistor

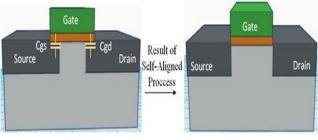

C. Why Polysilicon as Door Material One of the significant disadvantages of such a manufacture procedure is, to the point that if the entryway veil is misaligned, it makes a parasitic cover input capacitance Cgd and Cgs, as appeared in figure-2(a). The capacitance Cgd is more destructive in light of the fact that it is an input capacitance. Because of mill operator capacitance, there is a decrease in in the transistor's switching speed. Reducing Cgd and Cgs as shown in figure 2(b).

Figure 2. (a) Cgd – Cgs Parasitic Cpacitances, (b)

Reduced Cgd and Cgs as a result of Self aligned process

The doping process of the drain and source require very high temperature annealing methods (>8000\*C). If aluminum is used as a gate material, it would melt under such high temperature. This is on the grounds that the dissolving purpose of Al is around 660 degree C. Be that as it may, if polysilicon is utilized as an entryway material, it would not liquefy. In this way, the self-arrangement process is conceivable with polysilicon door. While on account of Al-entryway, it isn't conceivable, which results in high Cgd and Cgs. Undoped polysilicon has high resistivity, roughly 108 ohm/Cm. In this way, polysilicon is doped so that its obstruction is decreased.

The other purpose behind choosing poly is that the limit voltage of MOS transistor is associated with the work contrast between the door and the channel. Prior, metal doors were utilized while working voltages were in the scope of 3-5 volts. Yet, as the transistors were downsized, which guaranteed that the working voltages of the gadget were additionally cut down. A transistor with such high edge voltage progresses toward becoming non-operational under such conditions. Utilizing metal as door material brought about high limit voltage contrasted with polysilicon, since polysilicon would be of the equivalent or comparative piece as the mass Si channel. Additionally, as polysilicon is a semiconductor, its work capacity can be balanced by altering the level of doping.

# D. Working Principle of MOS:

For MOS transistor, the door voltage decides if a present stream between the deplete and source will occur or not. We should see further. At the point when an adequately positive Vgs voltage is connected to the doors of NMOS, the positive charges are set over the entryway as appeared in figure-3. These positive charges will repulse the minority bearers of ptype substrate i.e. openings from the substrate, abandoning negative charge acceptor particles which make exhaustion district. In the event that we increment Vgs further, at some potential level it will even make the surface alluring to electrons. In this way, a lot of electrons are pulled in to the surface. This circumstance is called reversal in light of the fact that the surface of p-type body regularly has countless yet the more current surfaces have a substantial quantities of electrons.

# III. TECHNOLOGY SCALING MOTIVATION

The interest for battery-worked compact devices have expanded step by step with huge amounts of uses including listening devices, mobile phone, workstations and so on. The "essential prerequisites" of such an application are less zone, bring down power utilization and less expensive advancement. For such versatile gadgets, control scattering is vital on the grounds that the power given by the battery is fairly restricted. Lamentably, battery innovations can't be relied upon to enhance the battery stockpiling limit by over 30% like clockwork. This isn't adequate to deal with the expanding power required in versatile gadgets.

In 1965, Gordon E. Moore anticipated that the quantity of transistors in a Coordinated Circuit will twofold at regular intervals (generally known as Moore's law). By making transistors littler, more circuits can be manufactured on the silicon wafer and in this manner, the circuit winds up less expensive. The decrease in channel length empowers quicker exchanging activities since less time is required for the current to spill out of deplete to source. At the end of the day, a littler transistor prompts littler capacitance. This causes a decrease in transistor delay. As unique power is relative to capacitance, the power utilization likewise lessens. This decrease of transistor measure is called scaling. Each time a transistor is scaled, we say another innovation hub has been presented. The base channel length of transistor is known as the innovation hub. For instance, 0.18 micrometer, 0.13 micrometer, 90 nanometers and so on. The scaling enhances cost, execution and power utilization with each new age of innovation.

### A POST TRADITIONAL SCALING INNOVAIONS

### A. Mobility Booster: Strained Silicon Technology

One of the key scaling issues in nano scale transistors is the portability corruption caused by the bigger vertical electric field. There are numerous approaches to upgrade transistor execution and portability. One path is to utilize thin germanium film in the channel since germanium has higher transporter portability. Another path is to utilize stressed silicon by presenting mechanical strain in the channel.

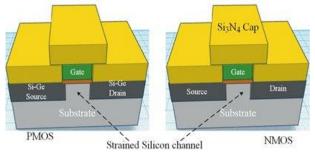

The stressed silicon innovation includes physically extending or packing the silicon precious stone utilizing different means, which thusly, expands bearer (electrons/openings) portability and upgrades the execution of the transistor. For instance, the gap portability of PMOS can be expanded when the channel is compressively focused. For making compressive strain in the silicon channel, the source and deplete areas are loaded up with Si-Ge film by an epitaxial development. Si-Ge commonly contains 20% germanium and 80% silicon blend. The quantity of Si and Ge molecules are equivalent to unique Si iotas. Germanium molecules are bigger than silicon particles. So when a power is made, it pushes the channel and raises the opening versatility. Expanding the portability of the semiconductor enhances drive current and transistor speed. The stressed silicon methods for MOS transistor were first utilized by Intel in their 90nm procedure innovation in 2003. In this innovation hub, the Si-Ge source deplete structure utilized for PMOS transistor incites compressive strain in the channel, enhancing current by 25%. While NMOS strain is presented by including high pressure Si3N4 topping layer around transistor, enhancing current by 10%.

# B. Gate Leakage Reduction: High-K Dielectric

The thickness of SiO2 (oxide) dielectric ought to be scaled in extent to its channel length. The 65nm hub, require Powerful Oxide Thickness (EOT) of around 2.3nm (real 1.6nm). In any case, if oxide thickness is decreased further underneath this point, the direct burrowing of bearer wonders will be prevailing. Because of this, the entryway spillage increments to an unsatisfactory farthest point. In this way, as far as possible for the oxide is around 1.6nm which is set by entryway to-channel burrowing spillage (additionally called quantum mechanical burrowing).

In the event that we take a gander at condition 1, the main alternative remaining is to choose dielectric material having high dielectric consistent (K) to expand the oxide capacitance. Since, thicker dielectric layers can be utilized, we get high entryway oxide capacitance. This thicker layer results in less bearer burrowing. SiO2has dielectric consistent of 3.9.

A leap forward in door oxide comes in 2007, the hafnium (HfO2) based High-K dielectric material was first presented by Intel in its 45nm high volume producing process. Hafnium material has dielectric consistent of roughly 25 which is 6 times higher than SiO2.

Figure 3. a) PMOS: Uniaxial Compressive Strain b) NMOS: Uniaxial Tensile Strain

High speed 12-bit ADCs have applications in communications, local area networks and flat panel displays

In CMOS, a simple methodology is to use a glimmer ADC. CMOS streak ADC's with exhibit averaging are accounted for to achieve a 1.3G examples/s change rate. Anyway the multifaceted nature of the glimmer ADC delivers exponentially as goals increments in light of the fact that the numeral of comparators increments by 2n (n is the goals of an ADC). a great deal of fast ADC structures have been accounted for to endeavor and vanquish the troubles of blaze ADCs

## IV. CONCLUTION AND FUTURE WORK

The Outline of pipeline ADC will be completed. The arrangement Outline segment is abridged as of now.

- ➢ 3-TIQ Comparator is utilized in single phase of ADC.

- > An Simple multiplexer is utilized as DAC.

- An OPAMP has been utilized in simple snake.

- A solidarity gain Modifying speaker is Outlined utilizing an OPAMP for test and hold circuit.

- > An Simple viper is planned utilizing OPAMP.

Shift enlist has been planned utilizing d flip-flounder. The general Outline will test with different info flags and check results.

### REFERENCES

- [1]. A Pipeline ADC for Very High Conversion Rates, Dante Gabriel Muratore, Edoardo Bonizzoni, Franco Maloberti Department of Electrical, Computer and Biomedical Engineering University of Pavia Pavia, Italy .IEEE 2016

- [2]. Low-Power Pipeline ADC for Wireless LANs J. Arias, V. Boccuzzi, L. Quintanilla,L. Enríquez, D. Bisbal, M. Banu, and J. Barbolla ieee 2014

- [3]. A 6 BIT 1.2 GSps low power flash ADC IN 0.13um digital cmos Martin clara andreas santner thamos hartig 2014

- [4]. A Pipeline Analogue to Digital Converter in 0.35 μm CMOS S.W. Ross<sup>†</sup>, StudenT Member, IEEE, and S. Sinha Member, IEEE 2012

- [5]. A 7 bit 16MS/s low power cmos pipeline ADC Zhuang zhaodong ,li zhiqug ieee 2011

- [6]. Y. Chang, C. Munoz, D. Daly, S.K. Shin, K. Guay, T. Thurston, H.S. Lee, K. Gulati, M. Straayer, "A 21mW 15b 48MS/s Zero-Crossing Pipeline ADC in 0.13μm CMOS with 74dB SNDR", IEEE International Solid State Circuits Conference (ISSCC) Dig. Tech. Pap., pp. 204-205, 2014.

- [7]. N. Dolev, M. Kramer, B. Murmann, "A 12-bit, 200-MS/s, 11.5-mW Pipeline ADC

- [8]. R.V.D Plassche, 'CMOS Integrated Analog to Digital and digital to Analog converters', 2nd edition: Kluwer Academic publisher, 2013

- [9]. K.Uyttenhove and M.S.J 'A 1.12-V 6-bit 1.3-GHz Flash ADC in 0.25µm CMOS' IEEE J.of solid-state circuit July 2011.