# Multi-Level Inverter For Domestic Application

Avinash. V M.Tech Student PES Institute of Technology Bangalore, India avinashvasu96@gmail.com

Raghumanth. A Research Associate PES Institute of Technology Bangalore, India raghumanth@yahoo.com

Venugopal.N Professor PES Institute of Technology Bangalore, India venugopaln@pes.edu

Abstract-In this paper both DC-DC Converter and multilevel inverter have been proposed. The proposed multilevel inverter with appropriate gate signals generates seven level AC output voltage. Also, with the implementation of Low Pass Filter, the output voltage's Total Harmonic Distortion is reduced. Not only switching losses but also voltage stress of switches can be reduced. With the help of Sinusoidal Pulse-Width Modulation (SPWM) switches of the inverters are controlled. Finally, a laboratory prototype has been implemented and from experimental results, the seven level output of implemented inverter can be inferred.

Keywords- THD, SPWM, FFT, MLI, MATLAB

#### INTRODUCTION L

Due to recent advancements in technology, the power quality demand is increasing daily. Inverter is nothing but a power device that converts DC to AC with the help of power electronic switches. Whenever the loads vary, the output frequency and voltage should change accordingly in order to satisfy different nature and demand of loads. In recent years power equipment has increased rapidly. In order to limit the harmonic quality and equipment's power factor, several standards and regulations have been formulated. In industrial sectors the demand for power applications and the power device's specification are higher. IGBT features not only high power rating but also high voltage stress. But the problem with them is that they cannot operate at high frequency. Further complexity is more while designing gate driver circuits for IGBT's. But even at higher frequency MOSFET can be able to operate, but power rating is not as good when compared.

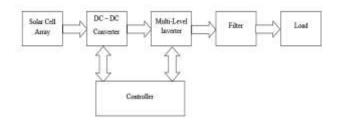

Both DC-DC Boost Converter and multilevel inverter has been presented. To achieve the required stepped level of output at the end of the load, multicarrier SPWM technique is used. Fig. 1 represents the block diagram of this project.

Figure 1. Block diagram of proposed system

#### II. PROPOSED SYSTEM

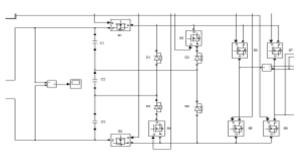

In this project, a general cascaded multilevel inverter using developed H-bridges has been proposed. This topology requires a lesser number of dc voltage sources and power switches and consists of lower blocking voltage on switches. This gives the advantage of decreased complexity and overall inverter cost. The proposed topology generates the required 7level voltage can be inferred both by simulation results and hardware prototype.

INDUCTOR DESIGN FOR PROPOSED BOOST CONVERTER II.

The design calculation are as follows:

### **Duty Cycle:**

$$D = 1 - \frac{V_{in}}{V_0} = 1 - \frac{25}{48} = 0.4791$$

So fixing Duty Cycle to 0.5

## **Efficiency:**

$\eta = \frac{Pout}{Pin} = \frac{70}{60} = 0.85 \text{ or } 85\%$

**Input Current Ripple:**  $\Delta I_L = 20\%$  of  $I_{in} = 2.8 * [\frac{20}{100}] = 0.56A$

**Output Voltage Ripple:**  $\Delta V_0 = 5\%$  of  $V_0 = 48 * [\frac{5}{100}] = 2.4 V$

Capacitor:  $C = \frac{I_{0.D}}{2.fs.\Delta V_0} = \frac{1.25*0.5}{2*20000*2.4} = 6.5 \mu F$

#### Inductor:

$$L = \frac{V_{in}.D}{fs.\Delta I_L} = \frac{25*0.5}{20000*0.56} = 1.11 \text{mH}$$

#### III. SIMULATION

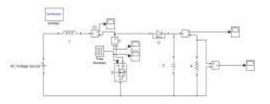

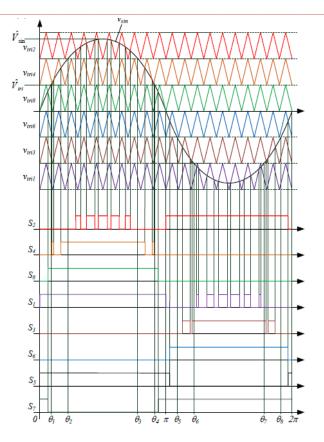

In this section of paper, both boost converter and inverter are simulated in MATLAB environment. The switches of the inverter are triggered using Multi carrier SPWM. The simulated results are as follows:

Figure 2. Boost converter

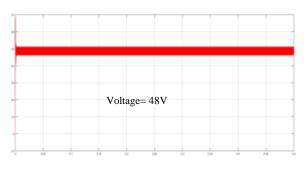

Figure 3. Output Voltage of Boost Converter

Figure 4. Seven Level Inverter

Figure 6. Reference sine wave, carriers, and control signals of switches.

**Operating Principles:**

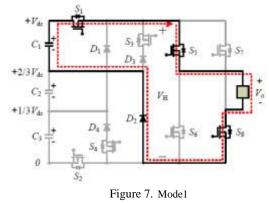

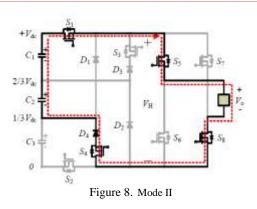

The required seven voltage output levels ( $\pm 1/3$ Vdc,  $\pm 2/3$ Vdc,  $\pm$ Vdc, 0) are generated as follows:

C1 provides the required energy while switches S1, S5 and S8 are turned on. As a result, (1/3) Vdc is obtained across the output terminals. Fig. 7 explains about this mode.

C1 and C2 provides the required energy while switches S1, S4, S5 and S8 are turned on. As a result, (2/3) Vdc is obtained across the output terminals. Fig. 8 gives the pictorial representation of this mode.

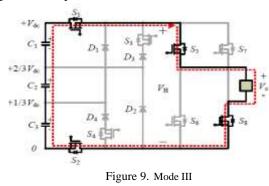

All the capacitors C1, C2 and C3 provides the required energy while switches S1, S2, S5 and S8 are turned on. As a result, +Vdc is obtained across the output terminals. Fig. 9 shows operation of this mode.

C3 provides the required energy while switches S2 (turned at negative cycle), S6 and S7 are turned on. As a result, -(1/3) Vdc is obtained across the output terminals. Fig. 10 explains working of this mode.

Figure 10. Mode IV

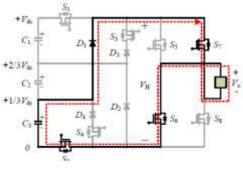

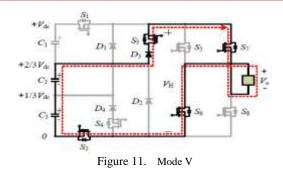

5) C2 and C3 provides the required energy while switches S2, S3, S6 and S7 are turned on. As a result, -(2/3) Vdc is obtained across the output terminals. Fig. 11 explains operation of this mode.

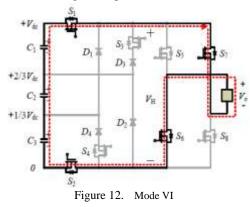

6) C1, C2 and C3 provides the required energy while switches S1, S2, S6 and S7 are turned on. As a result maximum negative peak (- Vdc) is obtained across the output terminals. Fig. 12 explains about this mode.

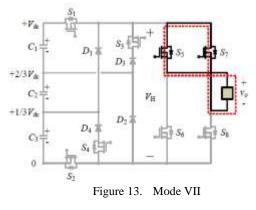

Here switches S5 and S7 are turned on. As a result V0= 0 is obtained across the output terminals. Fig. 13 gives pictorial explanation for this mode.

IV. HARDWARE RESULTS

#### **Boost Converter:**

Figure 14. Gate Pulse of Boost Converter

Fig. 14 represents the gating pulses for MOSFET before driver circuit. It's Switching Frequency (Fs) is 20 KHz and Duty cycle (D) is 50%.

| Tek      | n | Ting d | M P                          | os: 0.000s | CURSOR                    |  |

|----------|---|--------|------------------------------|------------|---------------------------|--|

|          |   |        |                              |            | Type<br>Amplitude         |  |

|          |   |        |                              |            | Source<br>EH1             |  |

|          |   |        |                              |            | -4¥ 48.8¥                 |  |

|          |   |        |                              |            | Cursor 1<br>48.8V         |  |

|          |   |        |                              |            | Cursor 2<br>0.00V         |  |

| 541-200V |   |        | M 25.0.us<br>30-May-17 10:42 |            | CH1 / 42.4V<br>28.3037MHz |  |

Figure 15. Output Voltage

Fig. 15 represents the output of the designed Boost Converter. Since the Solar supplies an input voltage of about 26V, the output voltage should be 52V. Due to drop in diode we are obtaining 48.8V.

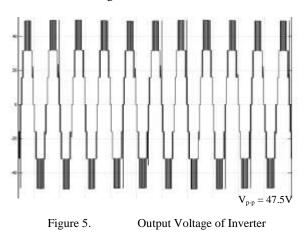

## **ProposedInverter:**

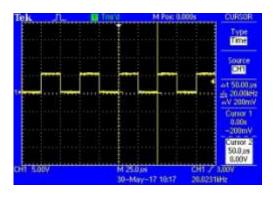

Fig. 16 represents the output of the designed inverter. As explained in simulation results, in hardware prototype also we are able to achieve the seven level output. The table 1 represents the time period of the obtained output.

Table 1 Time Period of Output waveform

| VOLTAGE LEVLS         | TIME PERIOD |

|-----------------------|-------------|

| V <sub>DC</sub>       | 6ms         |

| (2/3)V <sub>DC</sub>  | 2ms         |

| (1/3)V <sub>DC</sub>  | 1ms         |

| 0                     | 1ms         |

| -(1/3)V <sub>DC</sub> | 1ms         |

| -(2/3)V <sub>DC</sub> | 2ms         |

| -V <sub>DC</sub>      | 6ms         |

And this matches the simulation results.

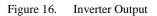

Figure 17. PWM Pulses

Fig. 17 represents the PWM pulses that is used for triggering the Switches S1, S2, S3, and S4 from the microcontroller. Here,

Yellow colored signal is the PWM pulse that is fed to Switch S1.

Green colored signal is the PWM pulse that is fed to Switch S2.

Blue colored signal is the PWM pulse that is fed to Switch S3. Pink colored signal is the PWM pulse that is fed to Switch S4.

When S1 is switched on PWM pulses are fed to S2 switch. And when S2 is turned on PWM pulses are fed to S1 switch respectively. Similarly, when S3 is turned off PWM pulses are fed to S4 and When S4 is turned off PWM pulses are fed to S3.

Figure 18. Pulses for H-Bridge

Fig. 5.16 represents the pulses for triggering the Switches S5, S6, S7, and S8, generated using Arduino Due. Here.

Yellow colored signal is the pulse that is fed to Switch S5. Green colored signal is the pulse that is fed to Switch S6. Blue colored signal is the pulse that is fed to Switch S7. Pink colored signal is the pulse that is fed to Switch S8.

To obtain 50 Hz output of the inverter, we operate these four switches at  $180^{\circ}$  phase shift with 10 ms each. Since S5 and S6 are in the same leg, we give inverted pulse to them to avoid the shorting of the switches. For same reason we give inverted pulse to S8 when compared to S7.

Figure 19. Harmonic analysis of Inverter

$$\mathrm{THD}_\mathrm{F} \;=\; rac{\sqrt{V_2^2 + V_3^2 + V_4^2 + \cdots}}{V_1}$$

THD

$$=\frac{\sqrt{((1.565)^2+(2.504)^2+(2.191)^2+(0.6)^2+(0.94)^2)}}{28.4}$$

= 0.135 or 13.5%

#### V. CONCLUSION

Hence using Boost Converter we are able to boost from the input Solar Voltage of 25V to 48V under open loop conditions. The boosted output is then fed to the inverter. We are able to achieve the seven level output both in simulation and hard ware prototype. The THD obtained from simulation and hardware prototype were 6.24% and 13.5% (without filter in hardware implementation) respectively.

#### REFERENCES

- E. Babaei, S. Alilu, and S. Laali, "A new general topology for cascadedmultilevel inverters with reduced number of components based on developed H-bridge", IEEE Trans. Ind. Electron., vol. 61, no. 8, pp. 3932–3939, Aug. 2014

- [2] M. F. Kangarlu and E. Babaei , "A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters", IEEE Trans. PowerElectron., vol. 28, no. 2, pp. 625– 636, Feb. 2013.

- [3] S. De, D. Banerjee, K. Siva Kumar, K. Gopakumar, R. Ramchand, and C. Patel, "Multilevel inverters for low-power application," IET Power Electron., vol. 4, no. 4, pp. 384–392, Apr. 2011

- [4] Ho-Dong Sun, Min-Young Park, Jong-Hyoung Park, Heung-Geun Kim, "Novel H-bridge Multi-level Inverter with DC- link Switches", 8<sup>th</sup> Internaltional Conference on Power Electronics – ECCE Asai May 30-June 3, 2011, The Shilla Jeju, Korea.

- [5] O. Lopez et al, "Comparison of a FPGA implementation of two multilevel space vector PWM algorithms", IEEE Trans. Ind. Electron., vol. 55, no. 4, pp. 1537–1547, Apr. 2008.

- [6] G. Ceglia, V. Grau, V. Guzman, C. Sanchez, F. Ibanez, J. Walter, A. Millan, and M. I.Gimenez, "A New Multilevel Inverter Topology," in Proc. Devices, Circuits and Systems, vol. 1, pp. 212-218, 2004.

- [7] Jinn-Chang Wu, Member, IEEE, and Kuen-Der Wu, "Five-Level Inverter for Renewable Power Generation System", Member, IEEE, (IEEE TRANSACTIONS ON ENERGY CONVERSION, VOL. 28, NO. 2, JUNE 2013)

- [8] H. D. Sun, M. Y. Park, J. H. Park, H. G. Kim, T. W. Chun, and E. C. Nho, "Novel H-bridge multi-level inverter with dc-link switches," in Proc. IEEE Int. Conf. Power Electron. ECCE Asia, 2011, pp. 1734–1741

- [9] Ravi Yadav, Praveen Bansal, "A Single-Phase Carrier Phaseshifted PWM Multilevel Inverter for 9-level with Reduced Switching Devices", International Journal of Science, Engineering and Technology Research (IJSETR), Volume 3, Issue 5, May 2014.

- [10] Napaphat Lekgamheng and Yuttana Kumsuwan "Phase-Shifted PWM Strategy of a Seven-level Single-Phase Current Source Inverter For Grid-Connected Systems," IEEE Trans. Ind. Appl. vol. 978-1-4673-1792-4/13 2013

- [11] Nami, F. Zare, G. Ledwich, A. Ghosh, and F. Blaabjerg, "Comparison between symmetrical and asymmetrical single phase multilevel inverter with diode-clamped topology," in

Proc.IEEE PowerElectron.Spec.Conf., Jun. 2008, p p. 2921–2926

- [12] M.ChithraandS. G. B.Dasan, "Analysis of cascaded H-bridge multilevel inverters with photovoltaic arrays," in Proc. Int. Conf. Emerging Trends Elect. Comput. Technol., Mar. 2011, pp. 442– 447.

- [13] J. Selvarai and N. A. Rahim, "Multilevel Inverter For Grid-Connected PV System Employing Digital PI Controller," IEEE Trans. on Industrial Electronics, vol. 56, no. 1, pp. 149158,2009.

- [14] G. P. Adam, S. J. Finnev, B. W. Williams, and M. T. Mohammed, "Two level operation of a diode-clamped

multilevel inverter."inProc.IEEEInt. Symp. Ind. Electron., Jul. 2010, pp. 1137–1142.

[15] G. P. Adam, S. J. Finnev, B. W. Williams, and M. T. Mohammed, "Two level operation of a diode-clamped multilevel inverter,"inProc.IEEEInt. Symp. Ind. Electron., Jul. 2010, pp. 1137–1142.